# Some pages of this thesis may have been removed for copyright restrictions.

If you have discovered material in Aston Research Explorer which is unlawful e.g. breaches copyright, (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please read our <u>Takedown policy</u> and contact the service immediately (openaccess@aston.ac.uk)

# A SIMULATION STUDY OF A LOCALISED COMPUTER NETWORK

Thesis submitted to the

UNIVERSITY OF ASTON IN BIRMINGHAM.

for the degree of

DOCTOR OF PHILOSOPHY

Zbigniew Ziemski

OCTOBER 1977

# A SIMULATION STUDY OF A LOCALISED COMPUTER NETWORK

#### SYNOPSIS

An investigation is carried out into the design of a small local computer network for eventual implementation on the University of Aston campus. Microprocessors are investigated as a possible choice for use as a node controller for reasons of cost and reliability. Since the network will be local, high speed lines of megabit order are proposed.

After an introduction to several well known networks, various aspects of networks are discussed including packet switching, functions of a node and host-node protocol. Chapter three develops the network philosophy with an introduction to microprocessors. Various organisations of microprocessors into multicomputer and multiprocessor systems are discussed, together with methods of achieving reliable computing. Chapter four presents the simulation model and its implementation as a computer program.

The major modelling effort is to study the behaviour of messages queueing for access to the network and the message delay experienced on the network. Use is made of spectral analysis to determine the sampling frequency while Exponentially Weighted Moving Averages are used for data smoothing.

Keywords: simulation, packet-switching, network,

microprocessor, fail-soft computing

#### ACKNOWLEDGEMENTS

I would like to express my gratitude to Dr. M. Walker for his guidance and supervision throughout the period of this research.

I am indebted to Mr. K. Bowcock for making available the facilities required to carry out this research. I would like to thank Mr. J. Hollingworth for the discussions with him and for his useful suggestions.

Finally, but not least, thanks are due to Miss S. Gaufroid for her very patient understanding and encouragement throughout the period of research and for typing the thesis under very difficult conditions.

|          | CONTENTS                               | Page |

|----------|----------------------------------------|------|

| Synopsia | S                                      |      |

| Acknowle | edgements .                            |      |

| Chapter  | One: Introduction to Computer Networks | 1    |

| 1.1      | Types of Networks                      | 2    |

| 1.2      | Existing Networks                      | 5    |

|          | 1.2.1 ARPA                             | 5    |

|          | 1.2.2 Cybernet                         | 10   |

|          | 1.2.3 DCS                              | 11   |

|          | 1.2.4 MERIT                            | 12   |

|          | 1.2.5 Octopus                          | 14   |

|          | 1.2.6 TSS                              | 16   |

|          | 1.2.7 TUCC                             | 17   |

| 1.3      | Modelling Methods                      | 19   |

| 1.4      | Objectives of Investigation            | 22   |

| Chapter  | Two: Functional Aspect of Networks     |      |

| 2.1      | Introduction                           | 26   |

| 2.2      | Packet-Switching                       | 26   |

|          | 2.2.1 Packet Format                    | 27   |

| 2.3      | Functions of a Node                    | 30   |

|          | 2.3.1 Message handling and buffering   | 31   |

|          | 2.3.2 Error Control                    | 32   |

|          | 2.3.3 Flow Control                     | 35   |

|          | 2.3.4 Routing                          | 41   |

| 2.4      | Host-Node Protocol                     | 45   |

| Chapter 5    | Three: Network Philosophy                       |     |

|--------------|-------------------------------------------------|-----|

| 3.1          | Introduction                                    | 48  |

| 3.2          | Microprocessors                                 | 49  |

| 3•3          | System Reliability                              | 56  |

| 3.4          | Network Design                                  | 61  |

| 3•5          | Node Functions                                  | 65  |

| Chapter      | Four: Network Model and Simulation Program      |     |

| 4.1          | Introduction                                    | 72  |

| 4.2          | Level of Simulation                             | 72  |

| 4.3          | Time Mechanism                                  | 74  |

| 4.4          | The Arrival Process                             | 76  |

| 4.5          | Hyper-Exponentially Distributed Message Lengths | 78  |

| 4.6          | Simulation Model                                | 80  |

| 4.7          | Processor Busy Time                             | 82  |

| 4.8          | Model Routines                                  | 83  |

| 4.9          | Simulation Program                              | 105 |

| 4.10         | Generating starting conditions                  | 105 |

| 4.11         | Generation of Pseudo-Random Numbers             | 107 |

| 4.12         | Simulation Program Printouts                    | 111 |

| Chapter      | Five: Effects of Parameter Changes in the Node  |     |

| 5.1          | Introduction                                    | 113 |

| 5.2          | Data Smoothing                                  | 113 |

| 5•3          | Selection of Sampling Frequency                 | 118 |

| 5.4          | Obtaining the Sampling Frequency                | 122 |

| 5 <b>•</b> 5 | Standard Network                                | 124 |

| 5.6             | Effects of the number of processors/memory modules          | 144 |

|-----------------|-------------------------------------------------------------|-----|

| 5•7             | Memory module size                                          | 153 |

| 5.8             | Conclusions                                                 | 161 |

|                 |                                                             |     |

| Chapter         | Six: High Level Network Parameters                          |     |

| 6.1             | Introduction                                                | 162 |

| 6.2             | Buffer Lockups                                              | 162 |

| 6.3             | Line utilisation                                            | 165 |

| 6.4             | Conclusions                                                 | 182 |

|                 |                                                             |     |

| Chapter         | Seven: Low Level Network Parameters                         |     |

| 7.1             | Introduction                                                | 197 |

| 7.2             | Packet Length                                               | 205 |

| 7•3 .           | Message Delay                                               | 213 |

| 7• <sup>4</sup> | Conclusions                                                 | 221 |

|                 |                                                             |     |

| Chapter         | Eight: General Conclusions and Suggestions for further work | 229 |

|                 |                                                             |     |

| Referenc        | es                                                          | 232 |

|                 |                                                             |     |

| Appendix        | I                                                           | 238 |

|                 |                                                             |     |

| Appendix        | : II                                                        | 242 |

|                 |                                                             |     |

| Appendix        | : III                                                       | 285 |

|              | LIST OF FIGURES                                        | Page         |

|--------------|--------------------------------------------------------|--------------|

| 1.1          | Centralised or star network                            | 3            |

| 1.2          | Distributed Network                                    | 4            |

| 1.3          | Ring Network                                           | 5            |

| 1.4          | Functional Units of ARPA Network                       | 7            |

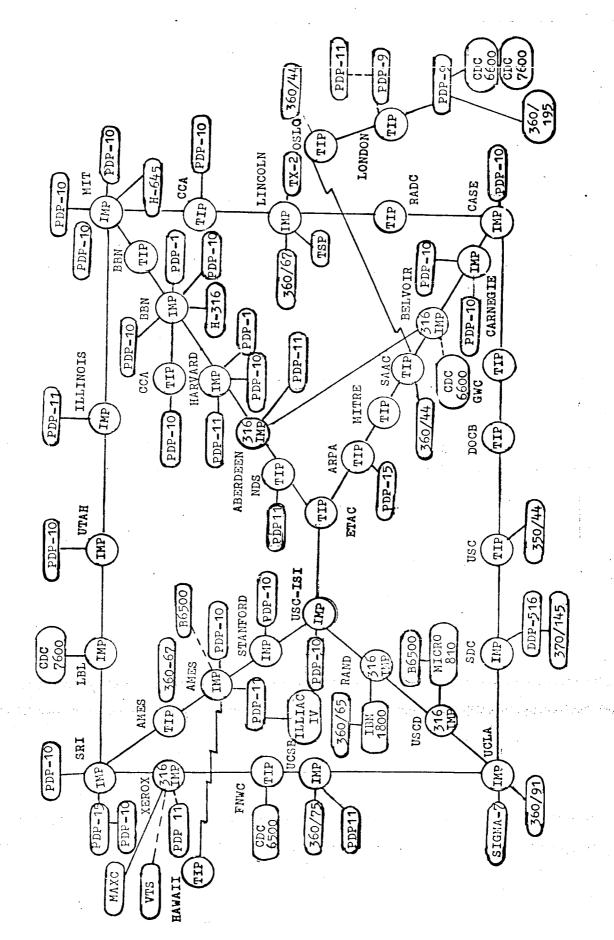

| 1.5          | ARPA network - logical map of hosts and nodes          | 9            |

| 1.6          | DCS network                                            | 11           |

| 1.7          | Merit Computer Network                                 | 13           |

| 1.8          | OCTOPUS network                                        | 15           |

| 1.9          | Features of Existing Networks                          | 20           |

| 1.10         | Type and Distribution of Computers at Aston University | 23           |

| 2.1          | Packet Format                                          | 28           |

| 2.2          | Packet Switching between host computers                | 33           |

| 2.3          | Reassembly Lockup                                      | 37           |

| 2.4          | Comparison of different Routing Strategies             | 44           |

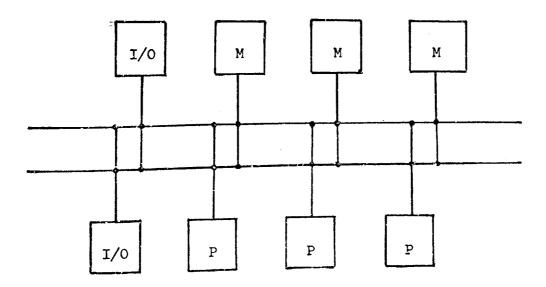

| 3.1          | Multicomputer System                                   | 51           |

| 3.2          | Multiprocessor System                                  | 52           |

| 3•3          | Master-Master Multiprocessor Organisation              | 5 <b>2</b>   |

| 3.4          | Master/slave Multiprocessor Organsiation               | 53           |

| 3 <b>•</b> 5 | Ring Multiprocessor System                             | 53           |

| 3.6          | Radial bus                                             | 54           |

| 3•7          | Time shared/common bus system - single bus             | 54           |

| 3.8          | Multiple time-shared/common bus system                 | 54           |

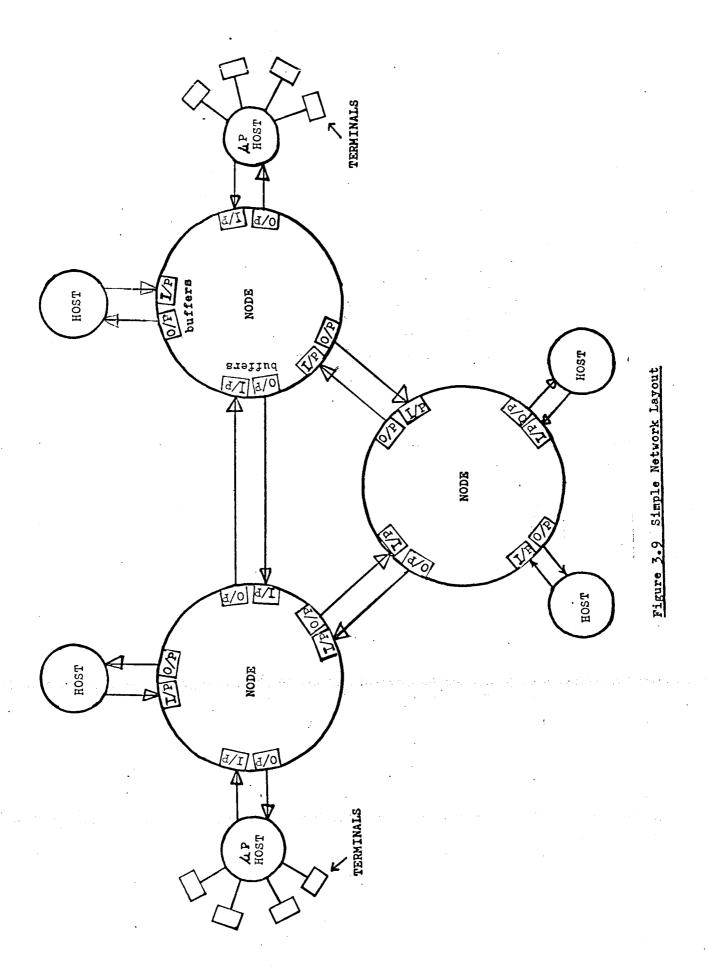

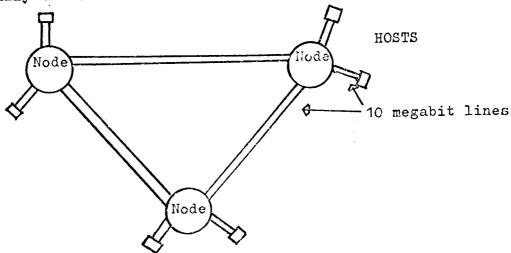

| 3.9          | Simple Network Layout                                  | 62           |

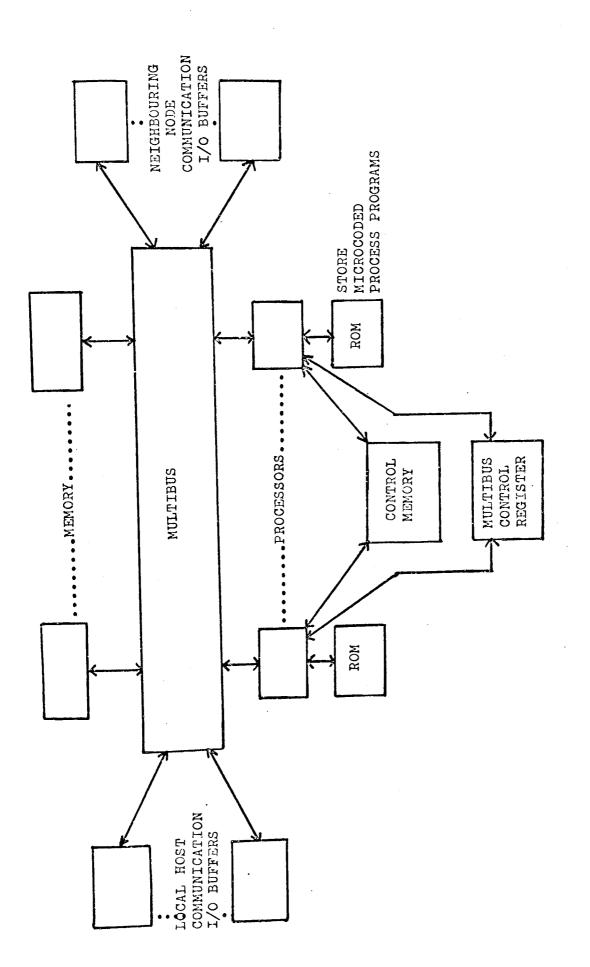

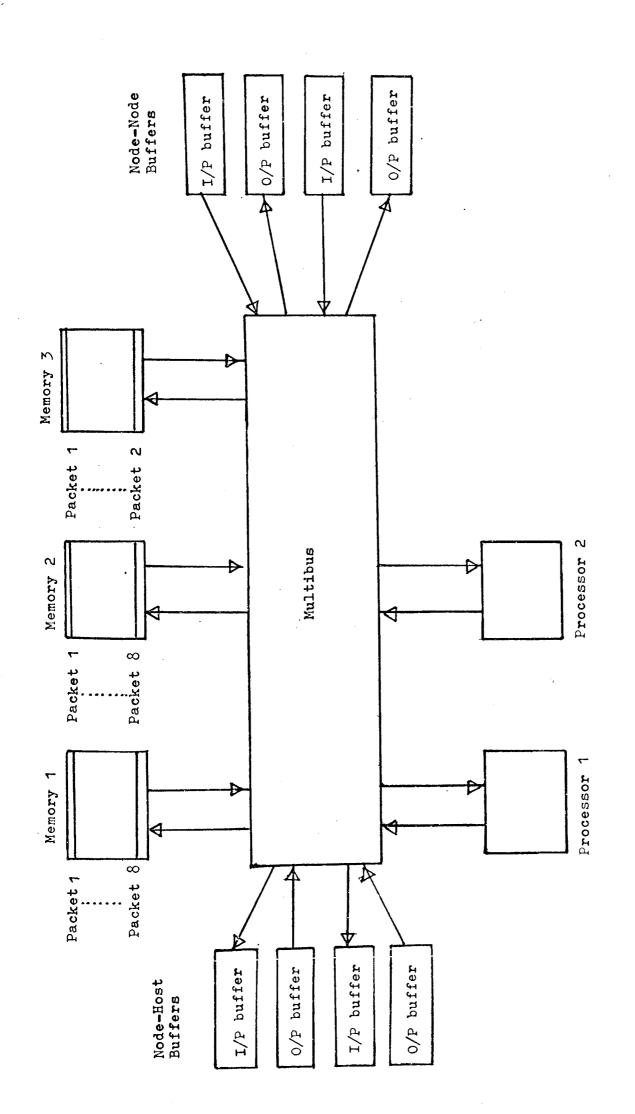

| 3.10         | Basic Node Architecture                                | 6 <i>t</i> i |

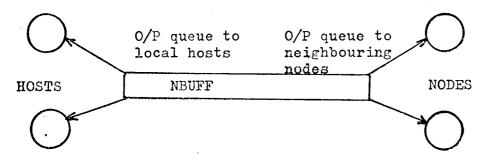

|   | 4.1  | Node queue handling                                                                                                  | 81  |

|---|------|----------------------------------------------------------------------------------------------------------------------|-----|

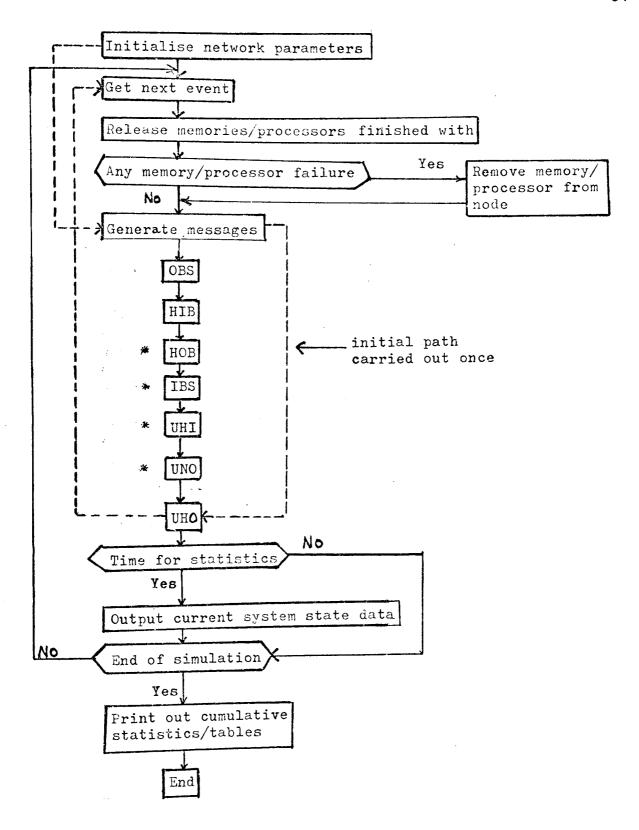

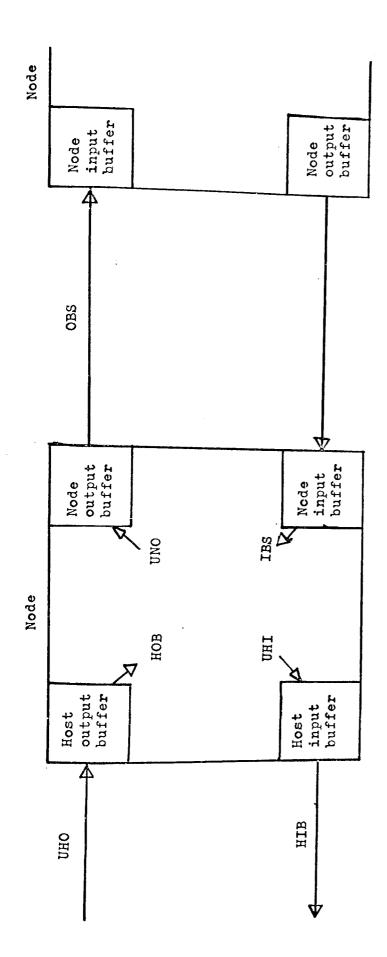

|   | 4.2  | Functional units of Simulation Model                                                                                 | 84  |

|   | 4.3  | Functional Units of the Simulation Model                                                                             | 86  |

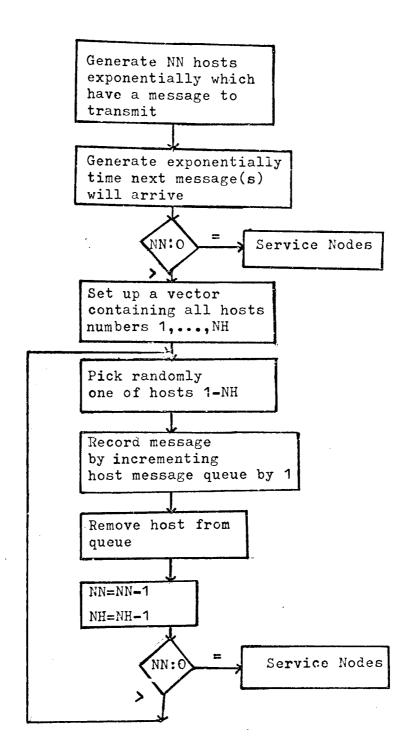

|   | 4.4  | Generation of Messages                                                                                               | 88  |

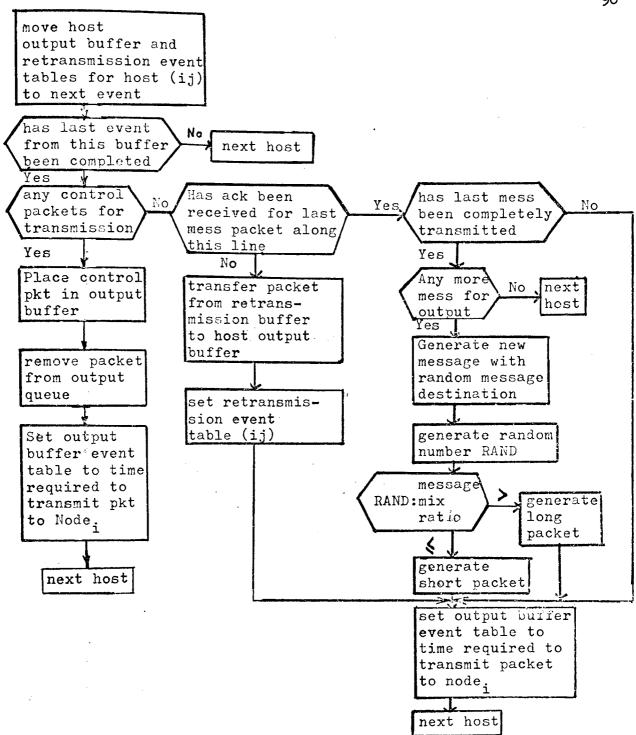

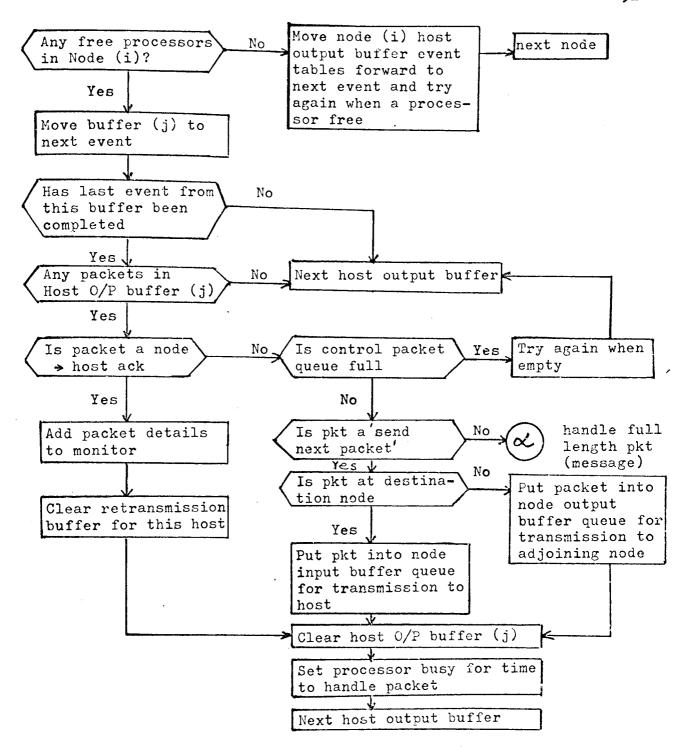

|   | 4.5  | Update host output buffer - node(i), host (j)                                                                        | 90  |

|   | 4.6  | Input packet from host (j) to node (i)                                                                               | 92  |

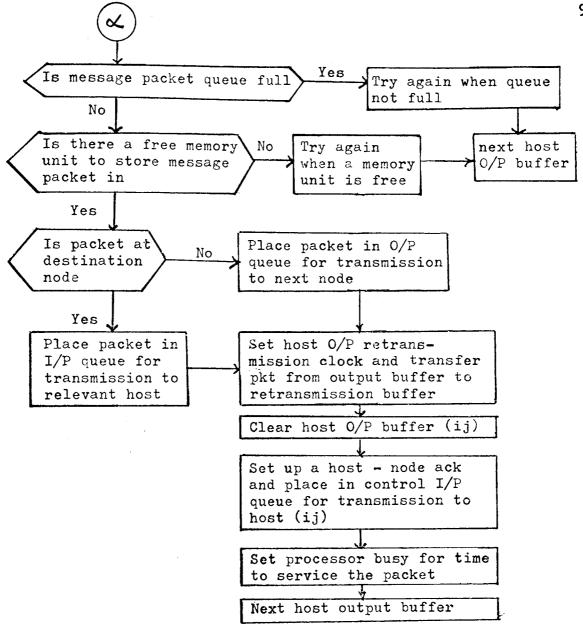

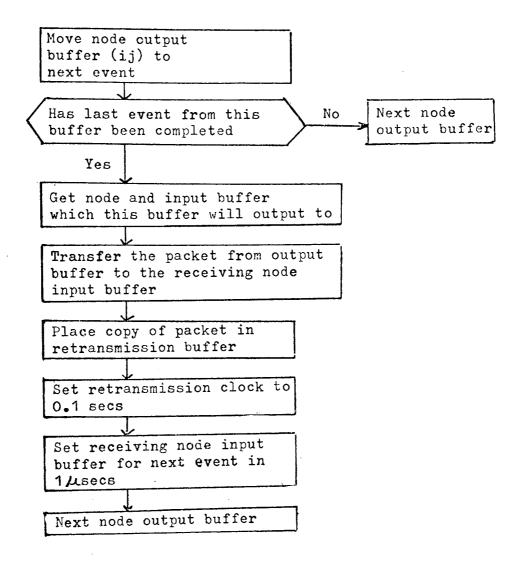

|   | 4.7  | Update node output buffers                                                                                           | 95  |

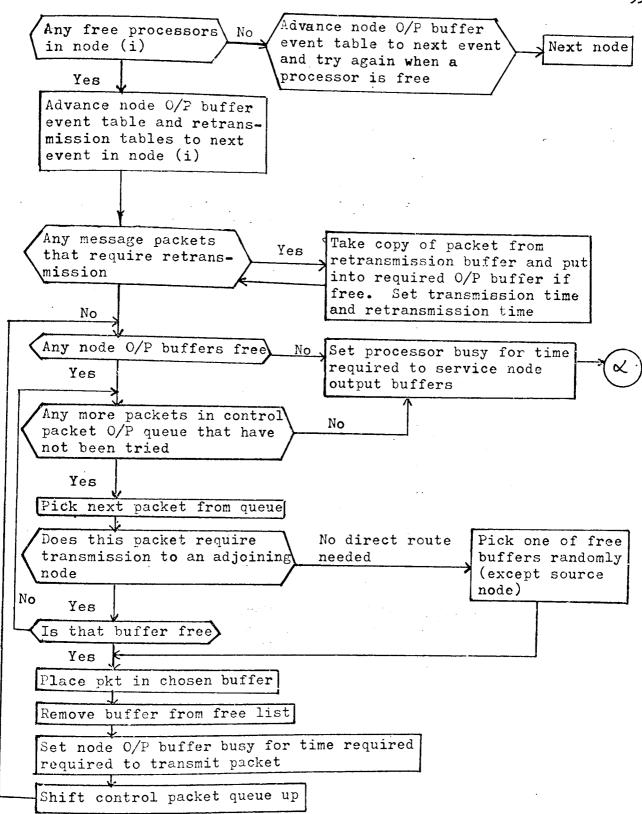

| , | 4.8  | Service node output buffer - node (i), host (j)                                                                      | 97  |

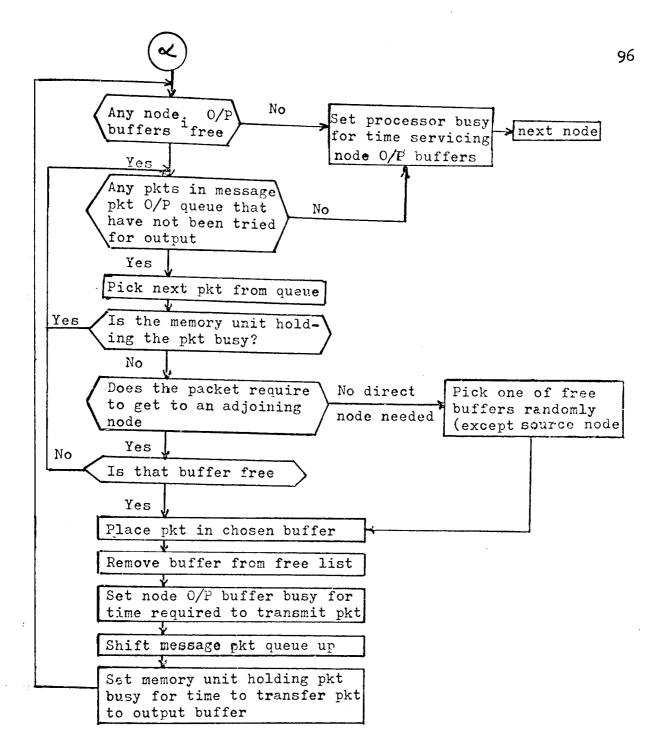

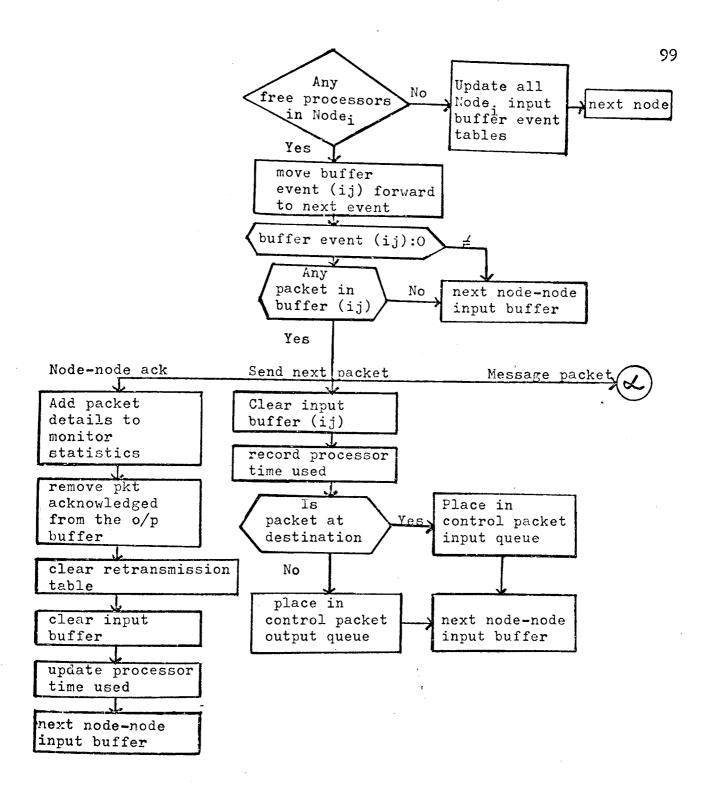

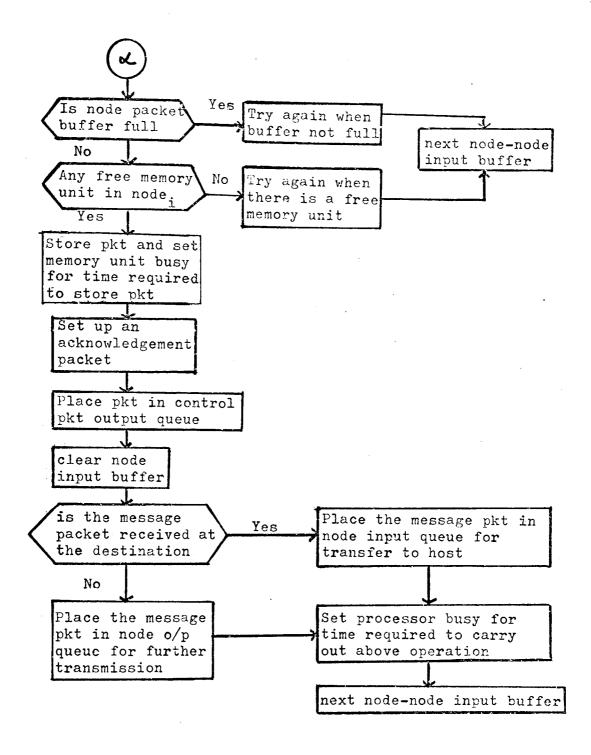

|   | 4.9  | Node-node input buffer service - node (i), Host (j)                                                                  | 99  |

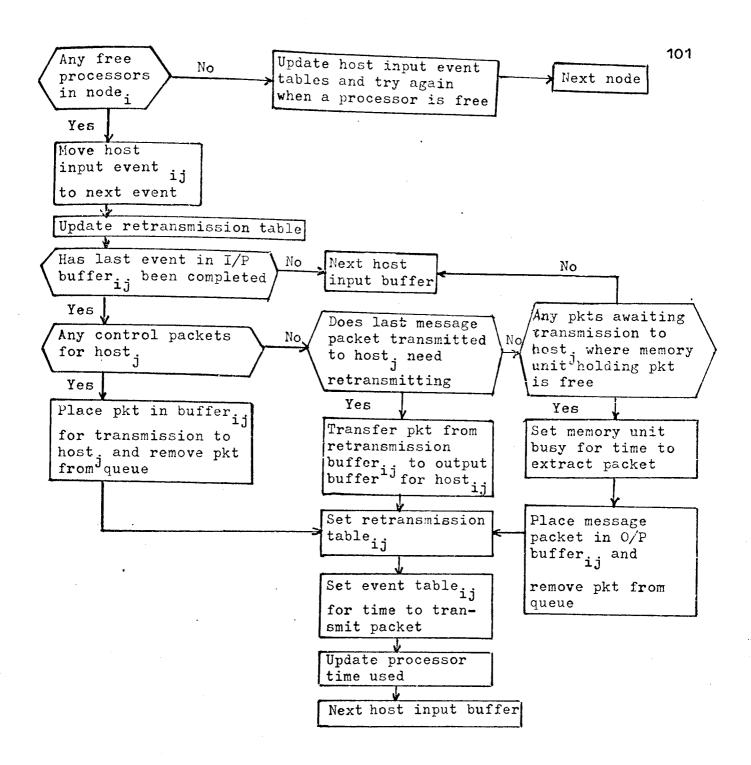

|   | 4.10 | Update host input buffer - node (i), host (j)                                                                        | 101 |

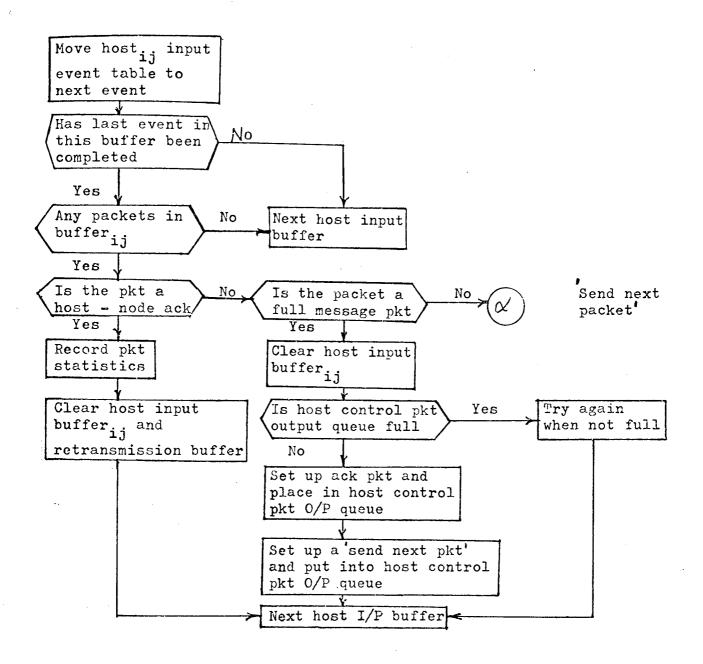

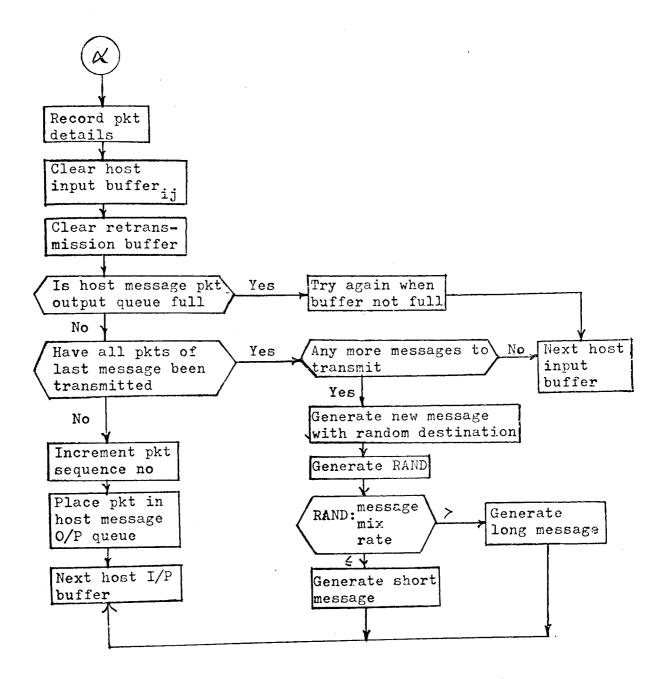

|   | 4.11 | Host input buffer service - node (i), host (j)                                                                       | 103 |

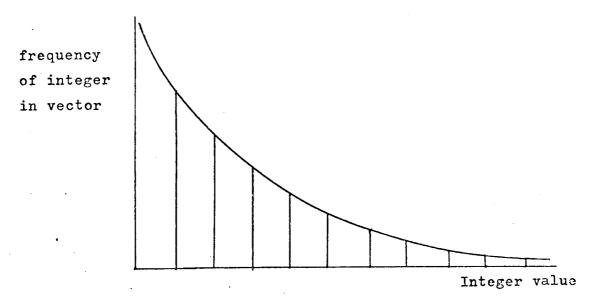

|   | 4.12 | Distribution of integers in sampling vector                                                                          | 108 |

|   | 4.13 | Part of E(t) distribution                                                                                            | 110 |

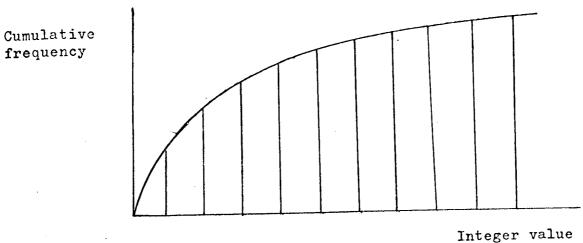

|   | 4.14 | Part of Cumulative frequency Distribution of E(t)                                                                    | 110 |

|   | 4.15 | Distribution of integers in Cumulative Frequency Table                                                               | 111 |

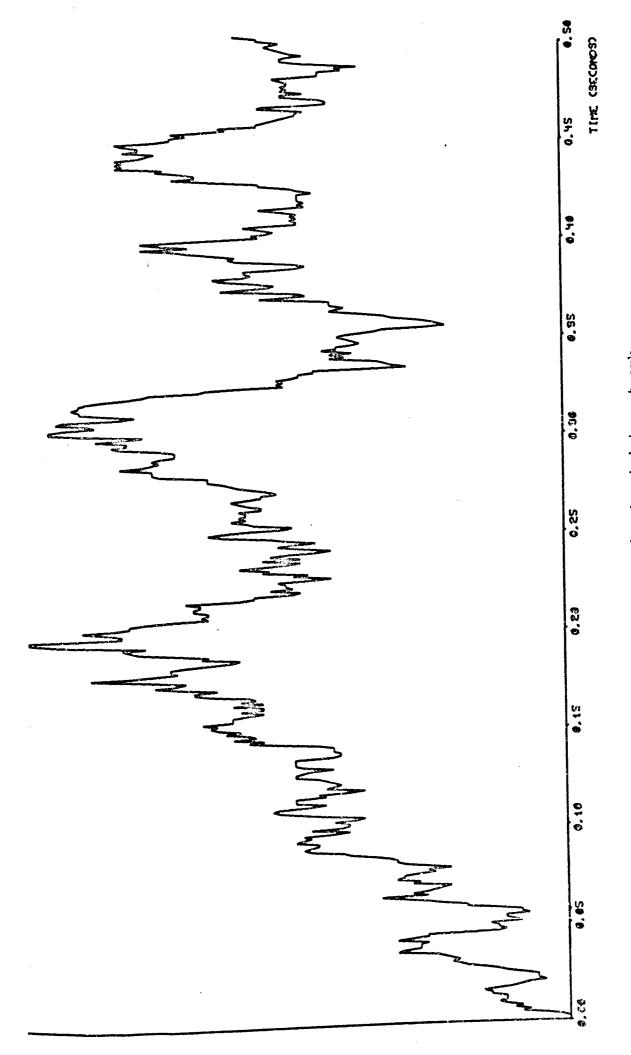

|   | 5.1  | Raw message queue for input into network                                                                             | 115 |

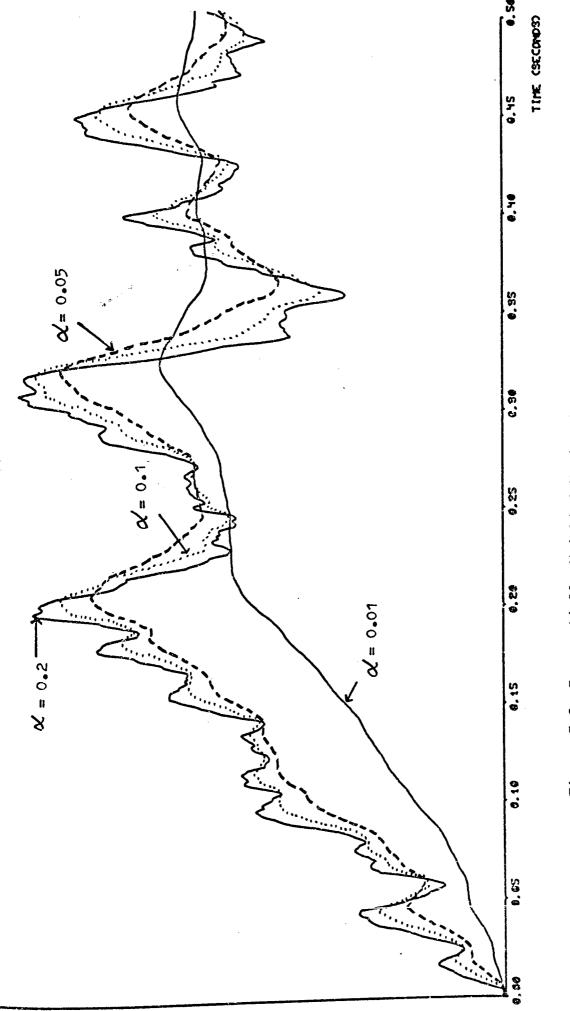

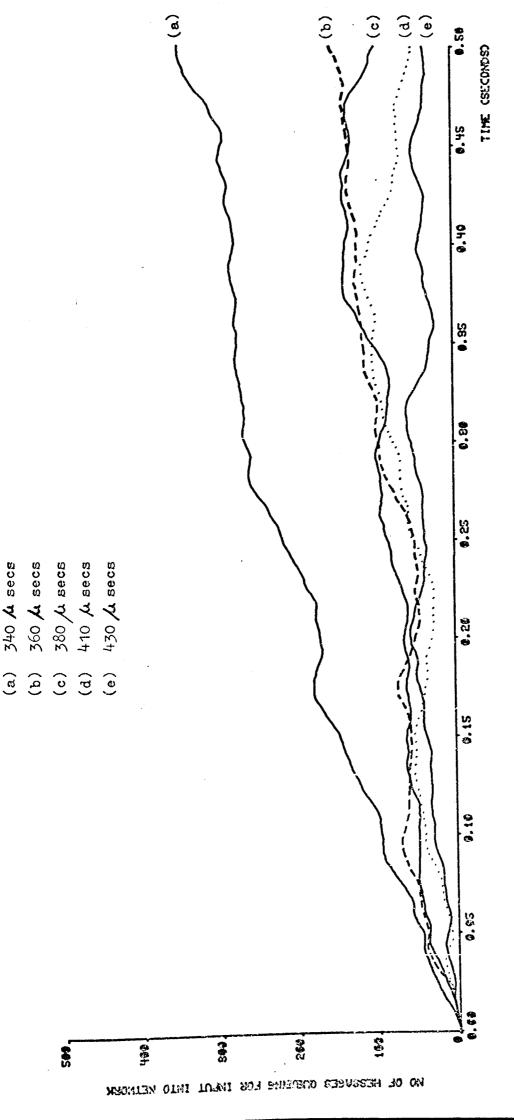

|   | 5•2  | Exponentially Weighted Moving Average of message queue for input into network, with $\alpha = 0.01$ , 0.05, 0.1, 0.2 | 117 |

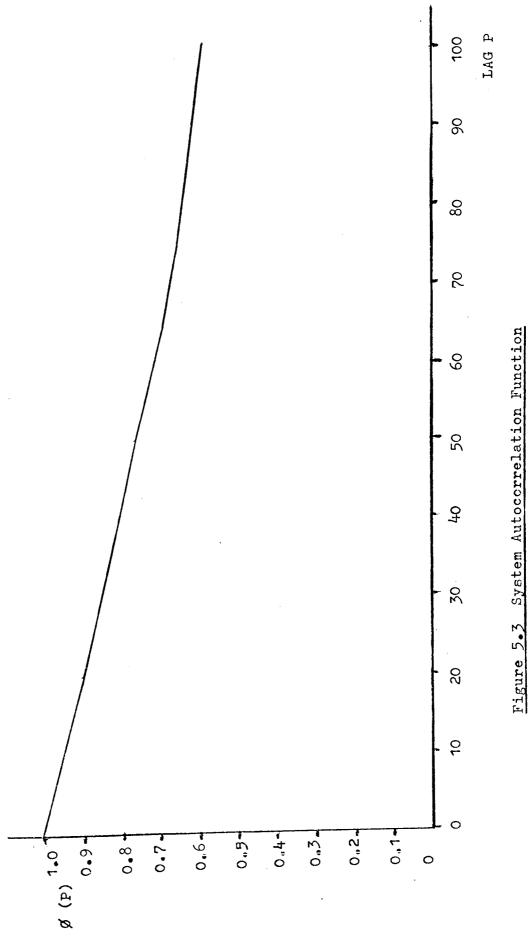

|   | 5•3  | System Autocorrelation Function                                                                                      | 121 |

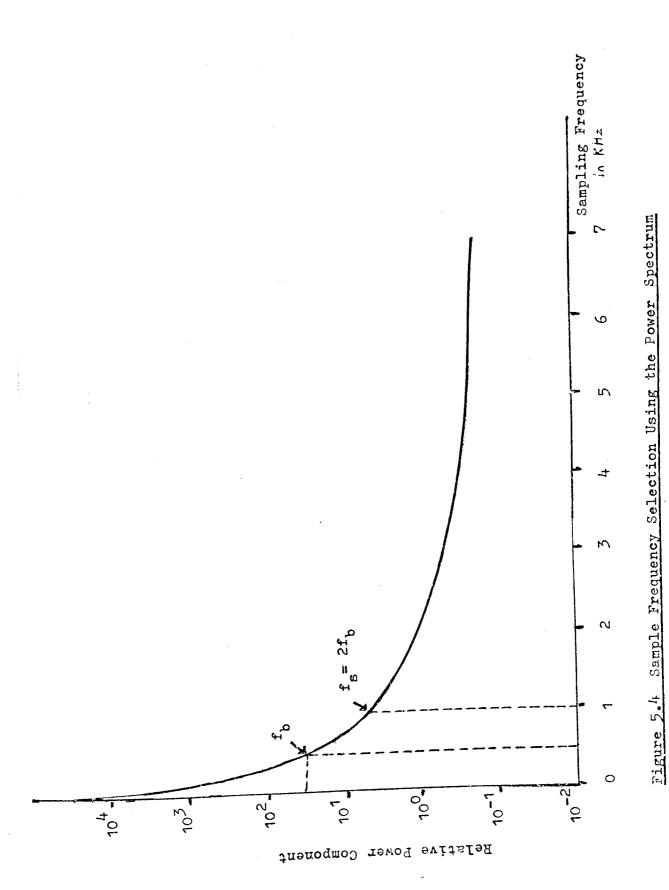

|   | 5.4  | Sample Frequency Selection Using the Power Spectrum                                                                  | 123 |

|   | 5•5  | Standard Network                                                                                                     | 124 |

|   | 5.6  | Standard Network: Node Architecture                                                                                  | 126 |

|   |      | Standard Network                                                                                                     |     |

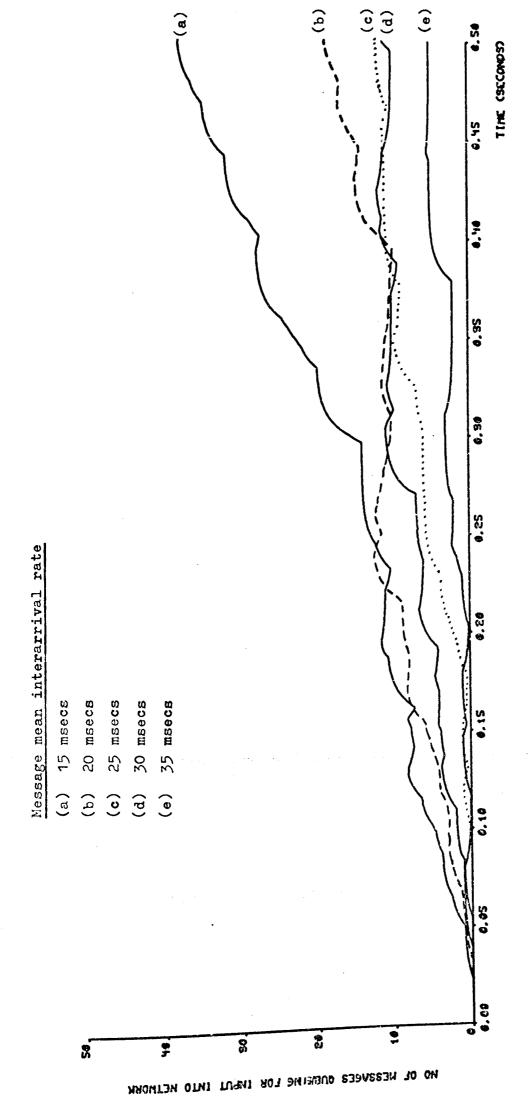

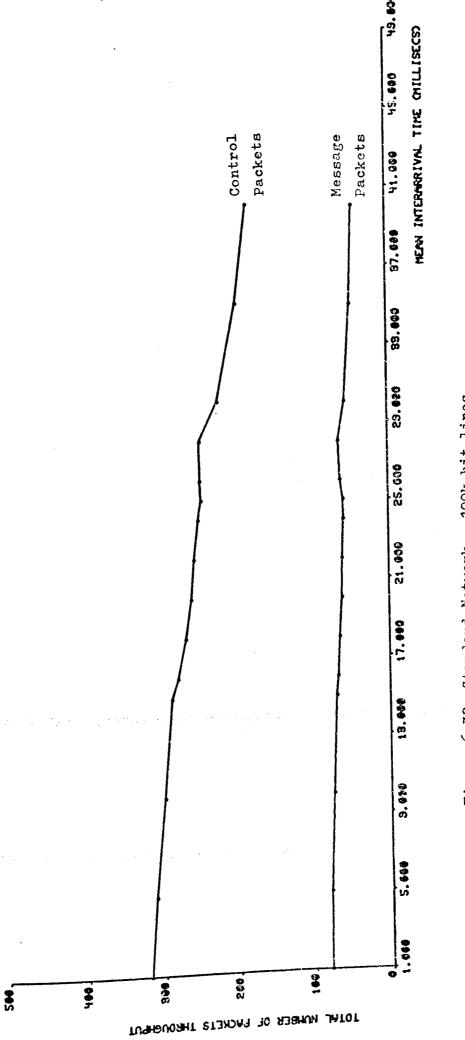

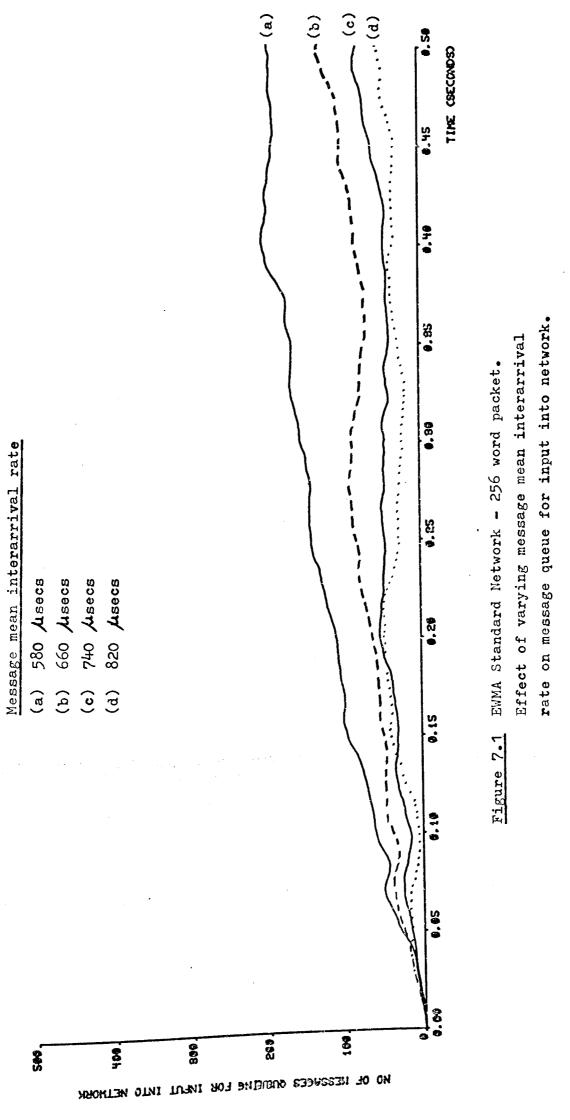

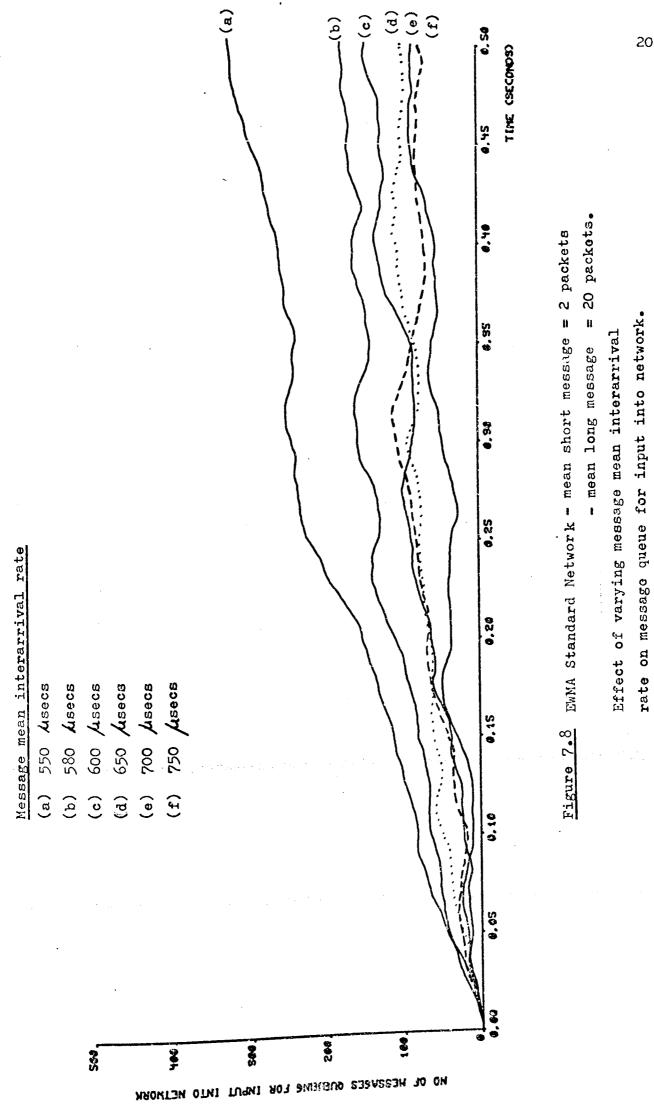

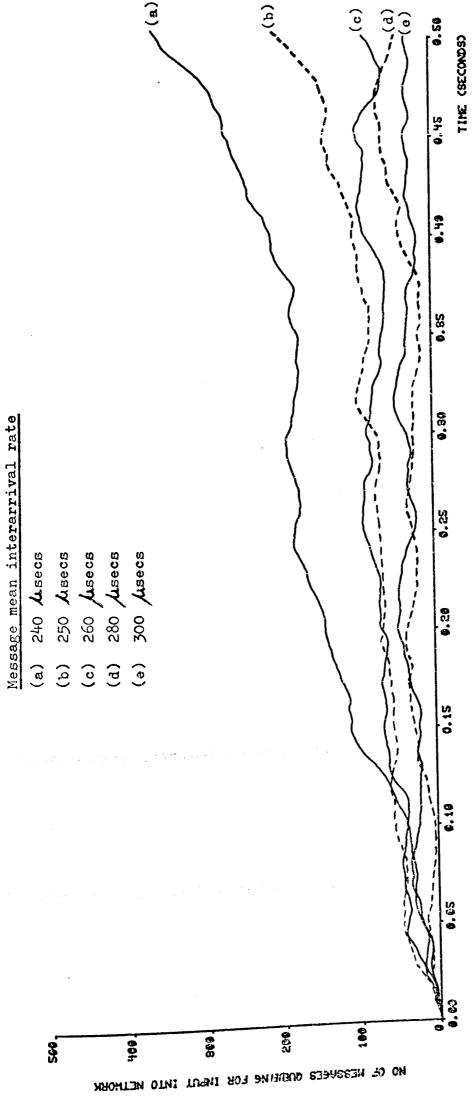

|   | 5•7  | Effect of varying message mean interarrival rate on message queue for input into network                             | 128 |

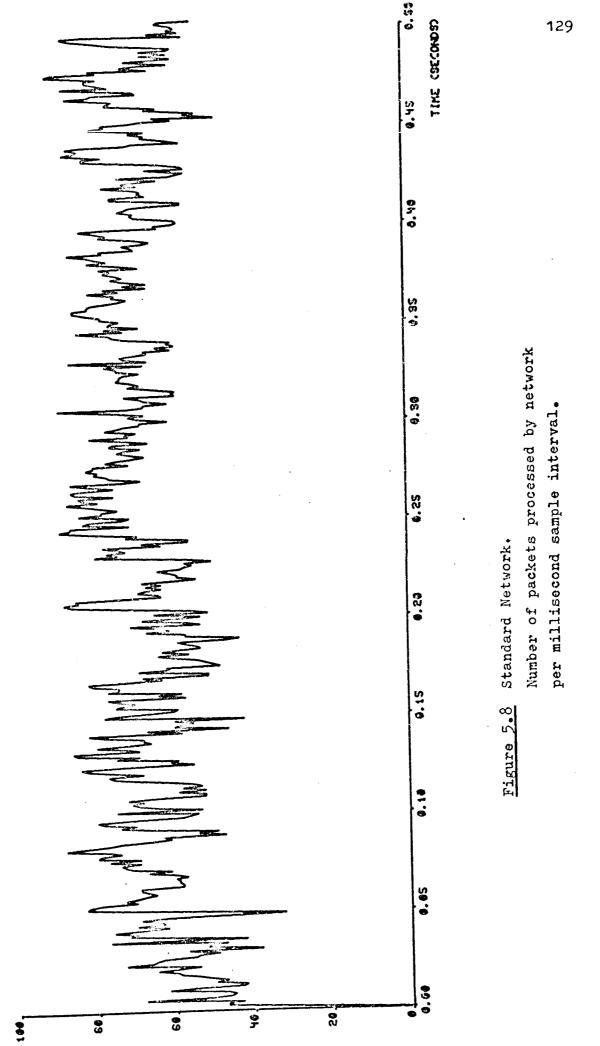

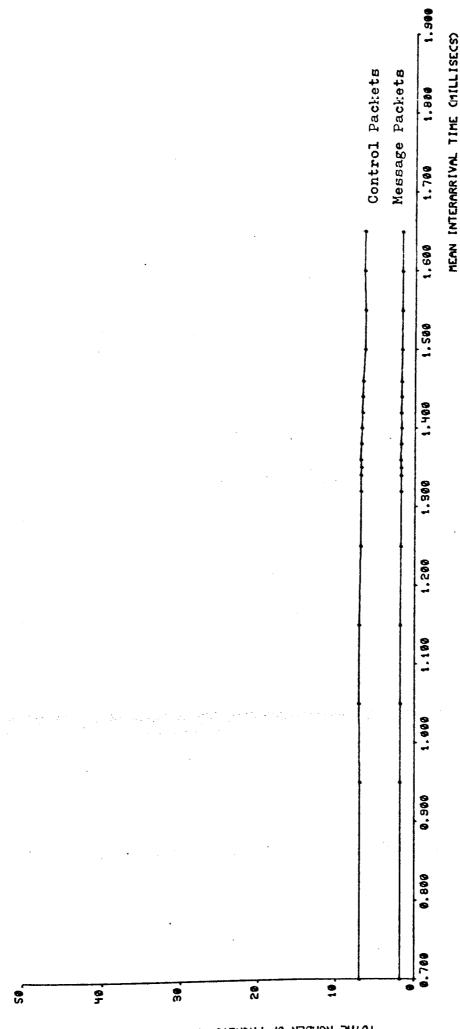

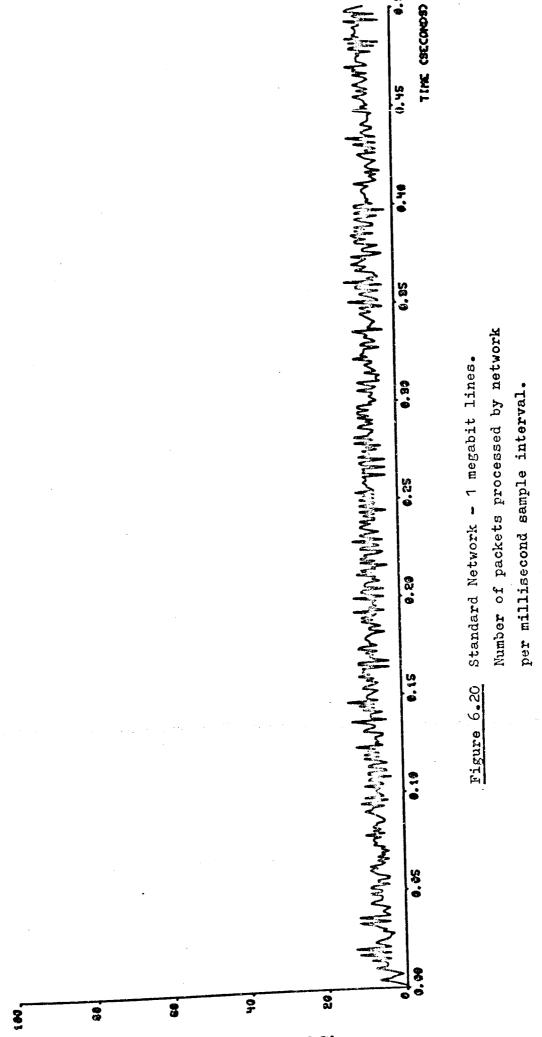

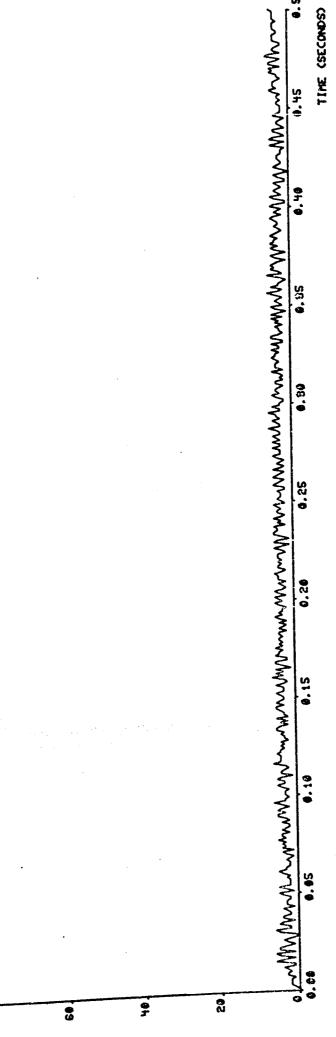

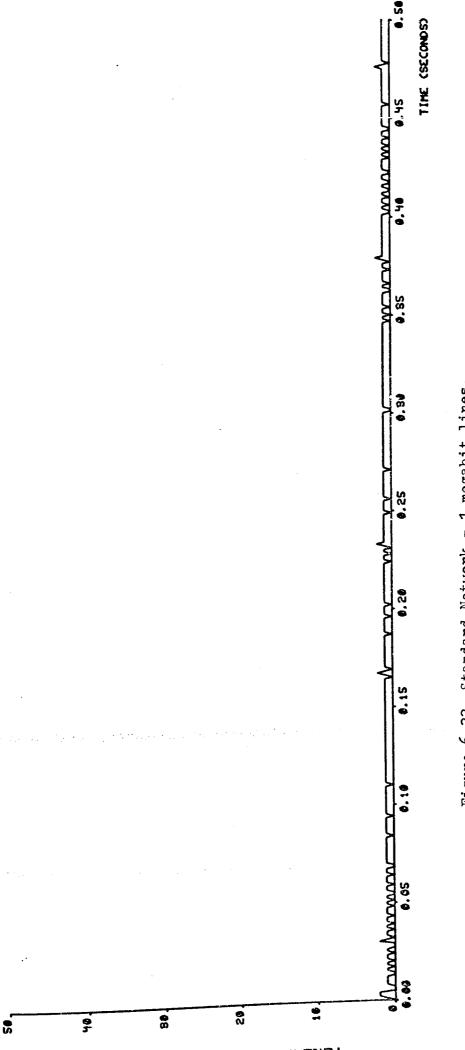

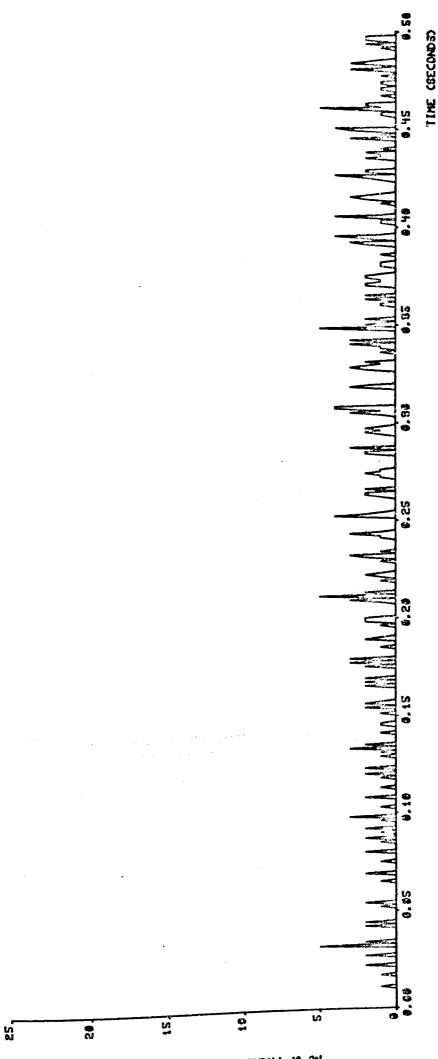

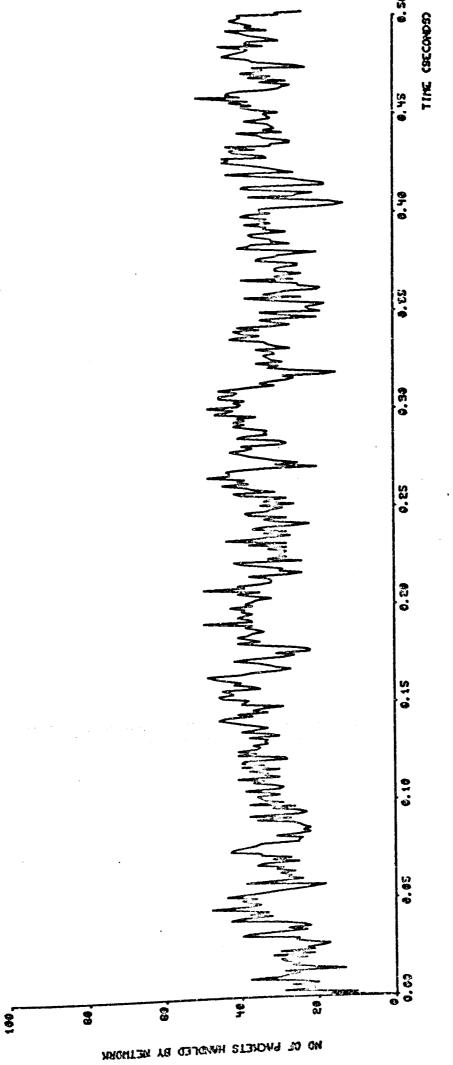

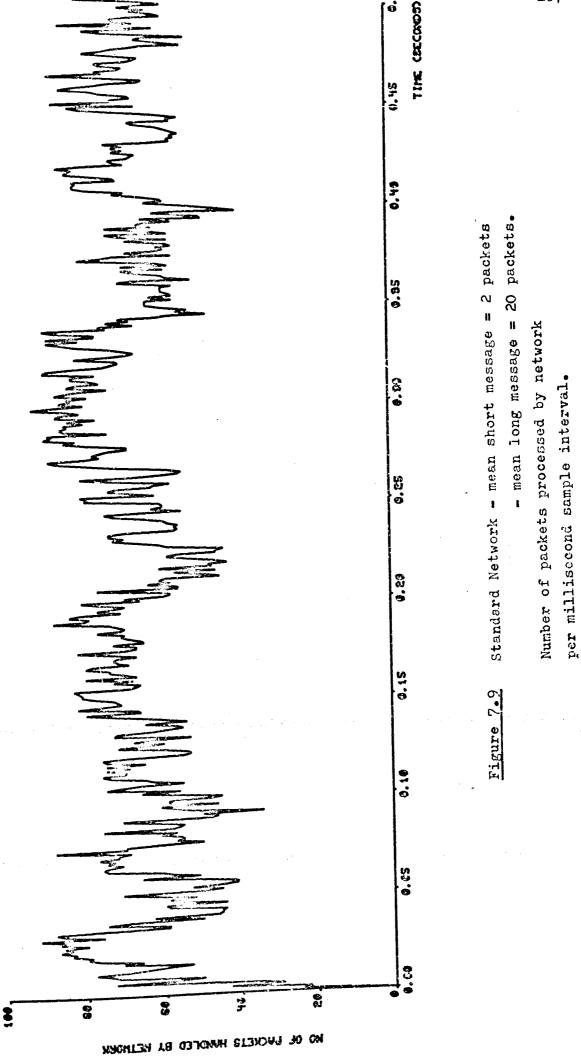

|   | 5.8  | Number of packets processed by network per millisecond sample interval                                               | 129 |

|   |      | ·                                                                                                                    |     |

•

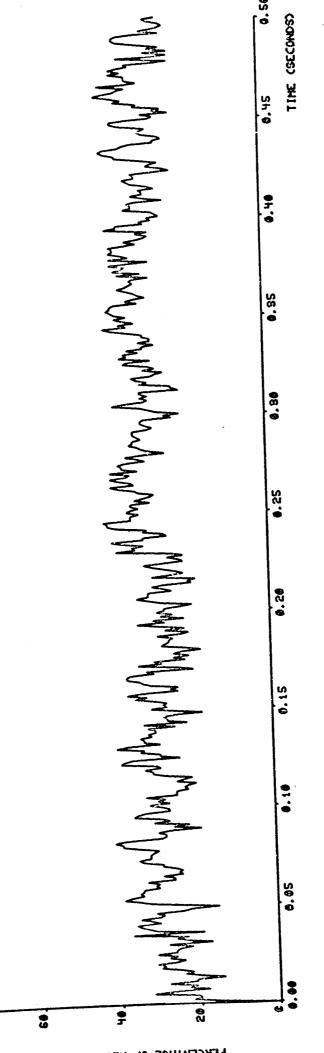

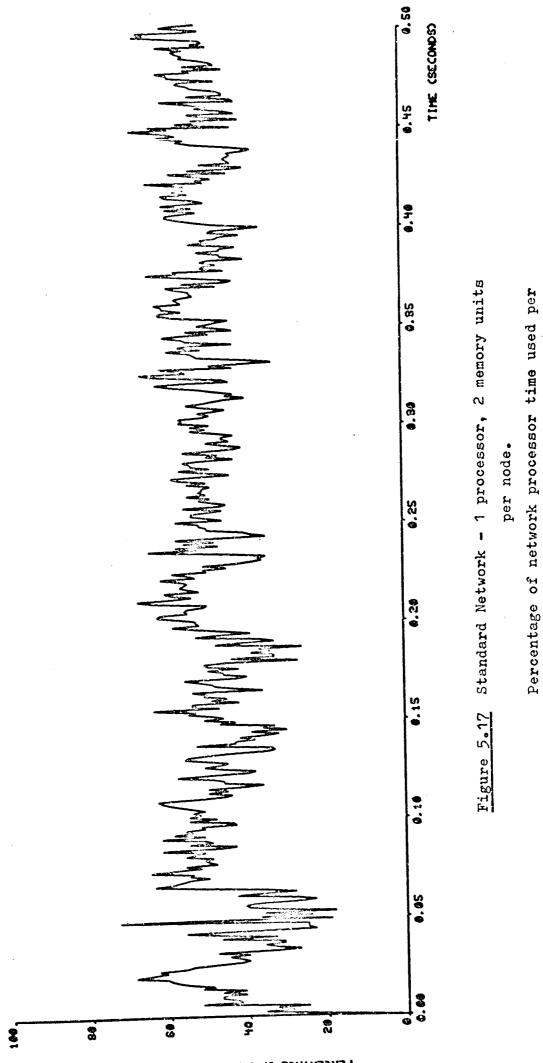

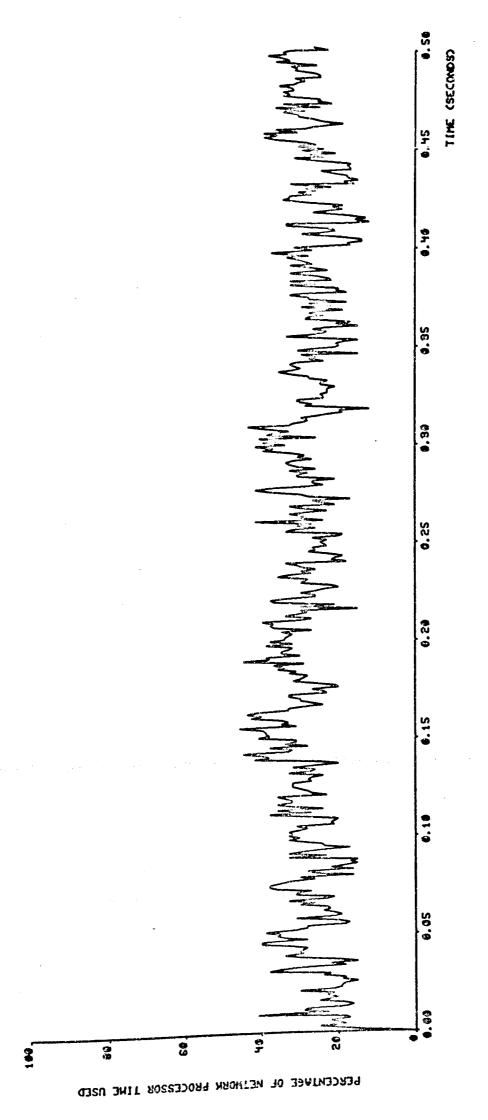

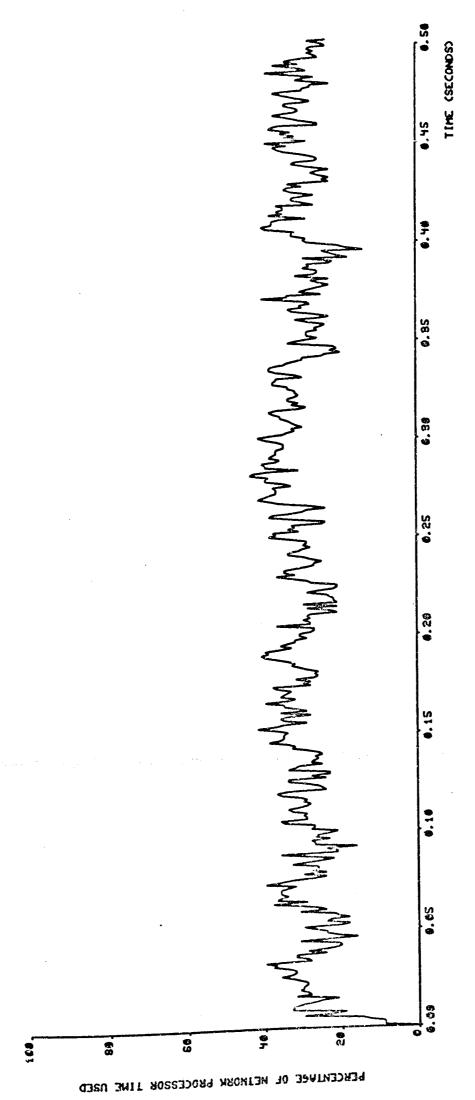

| 5•9          | Percentage of network processor time used per millisecond sample interval                | 130         |

|--------------|------------------------------------------------------------------------------------------|-------------|

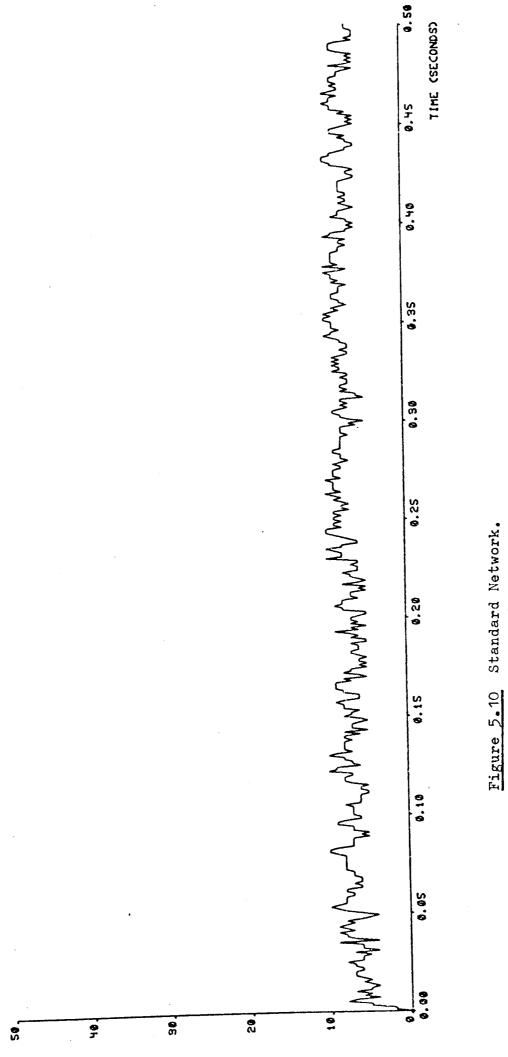

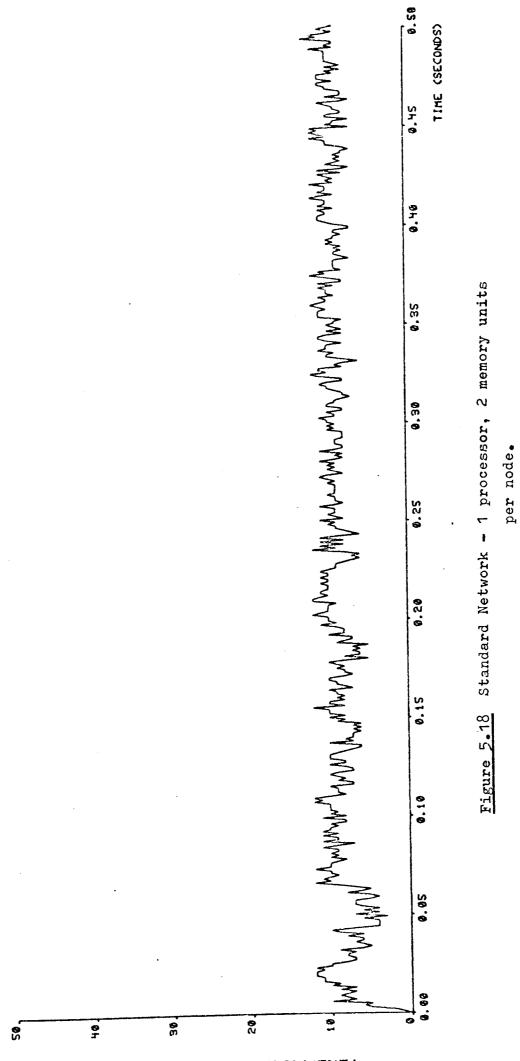

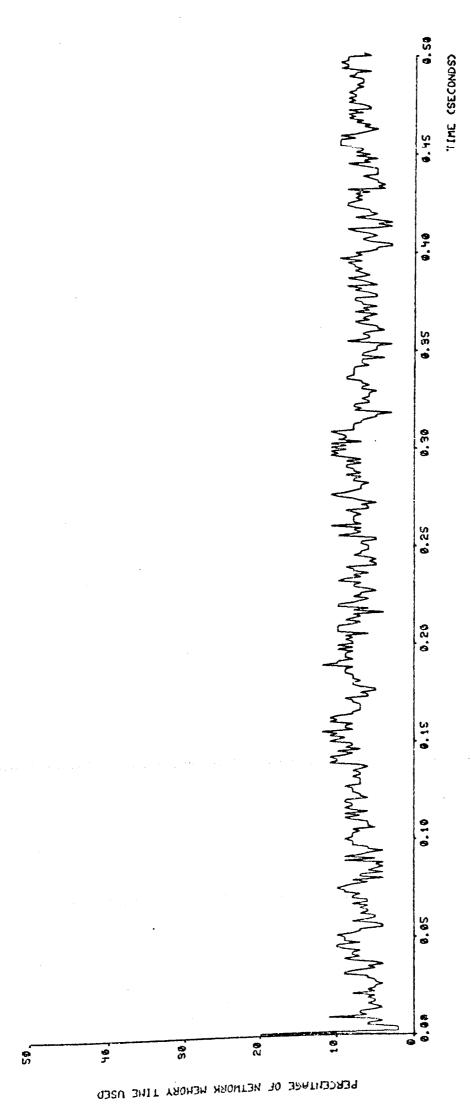

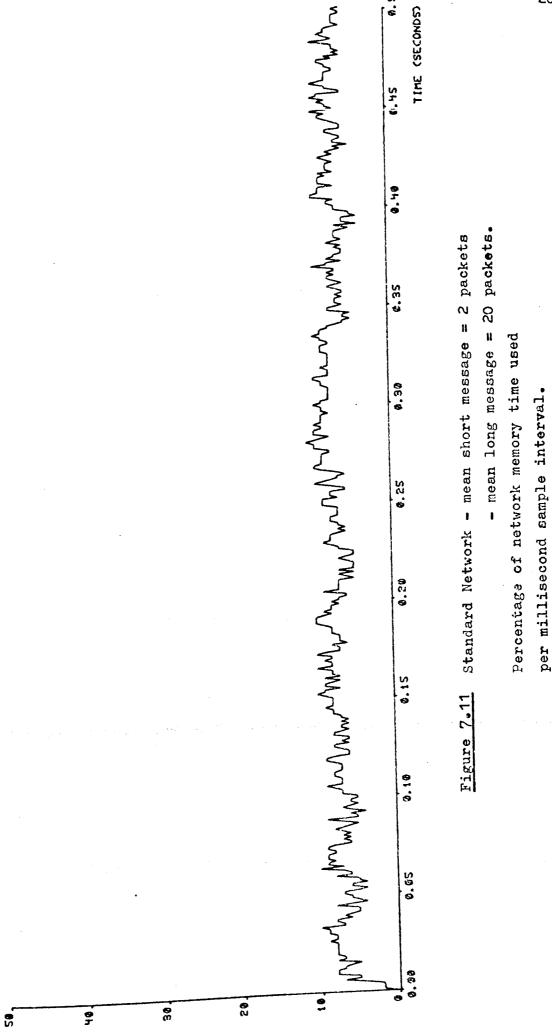

| 5.10         | Percentage of Network Memory time used per millisecond sample interval                   | 131         |

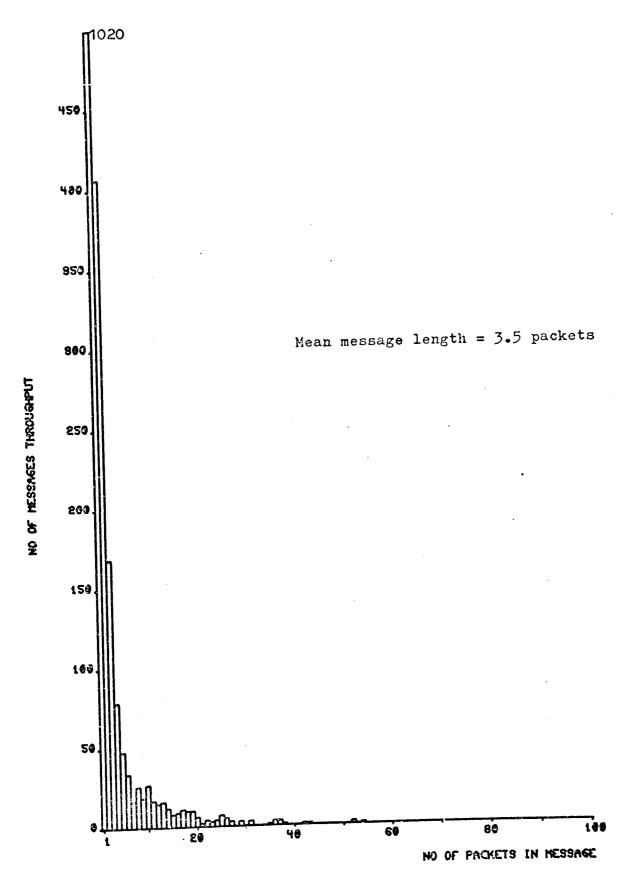

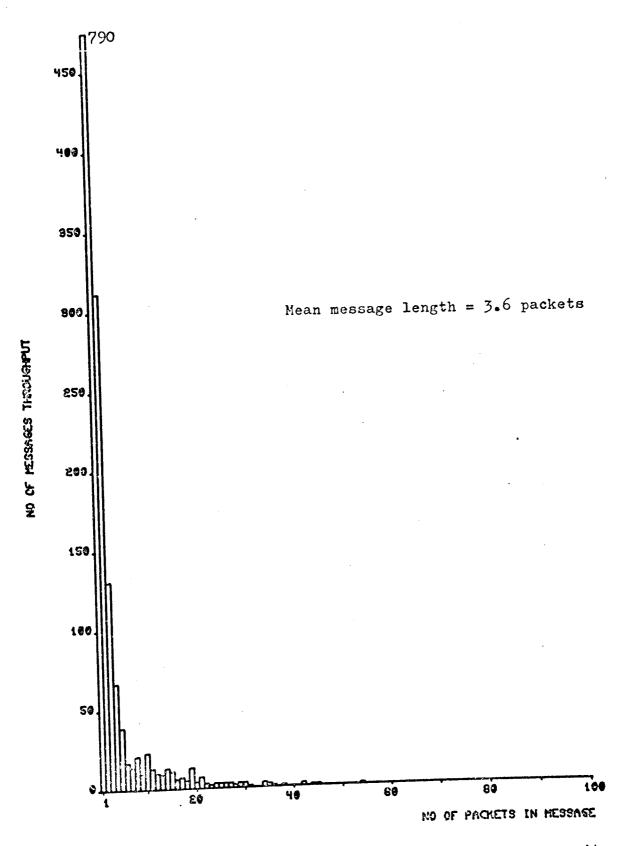

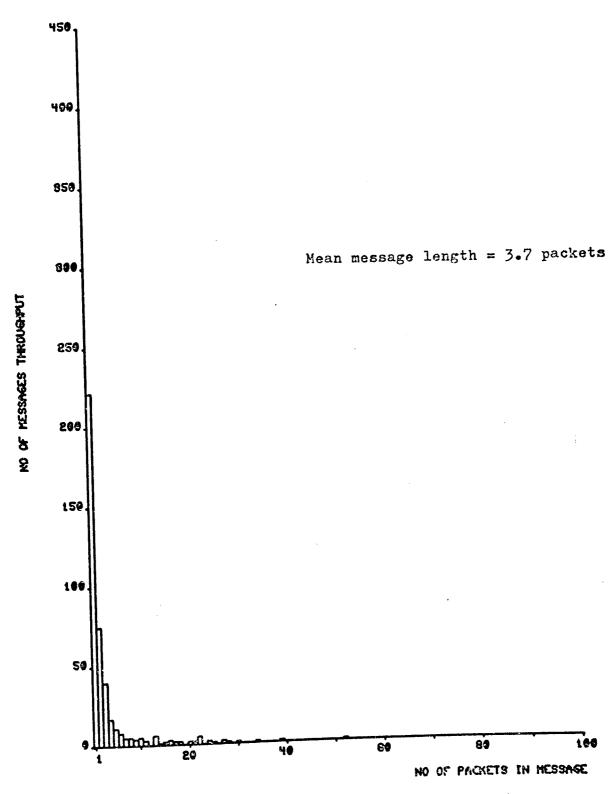

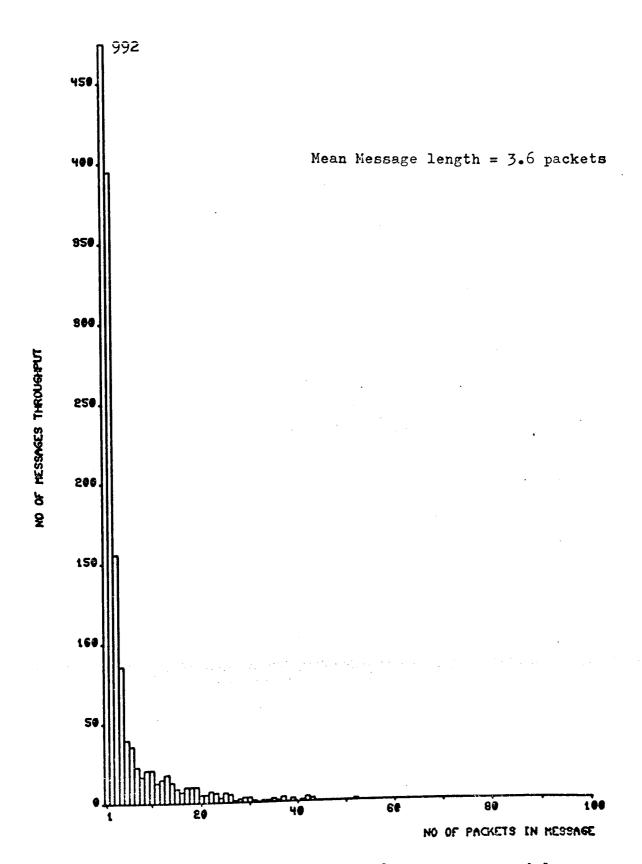

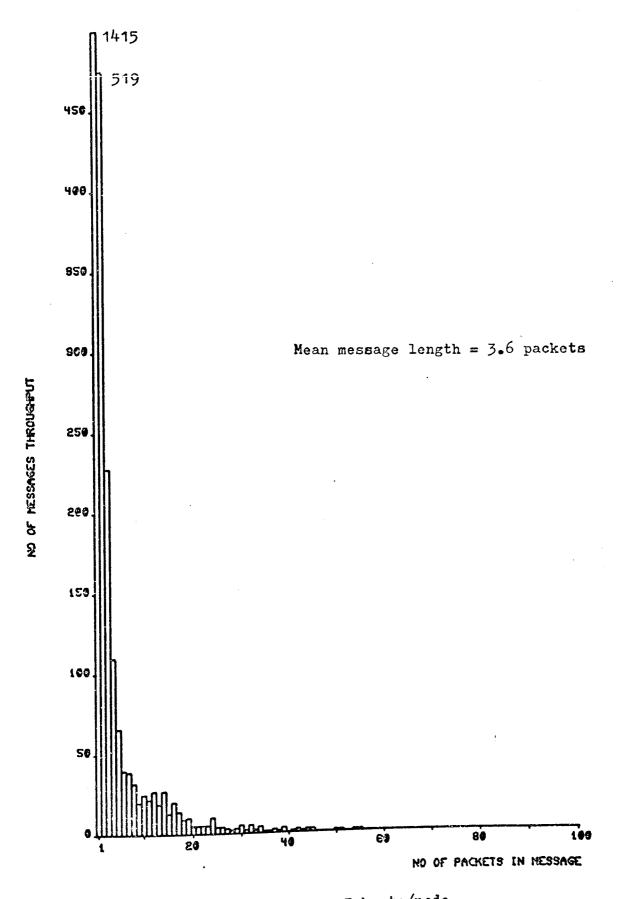

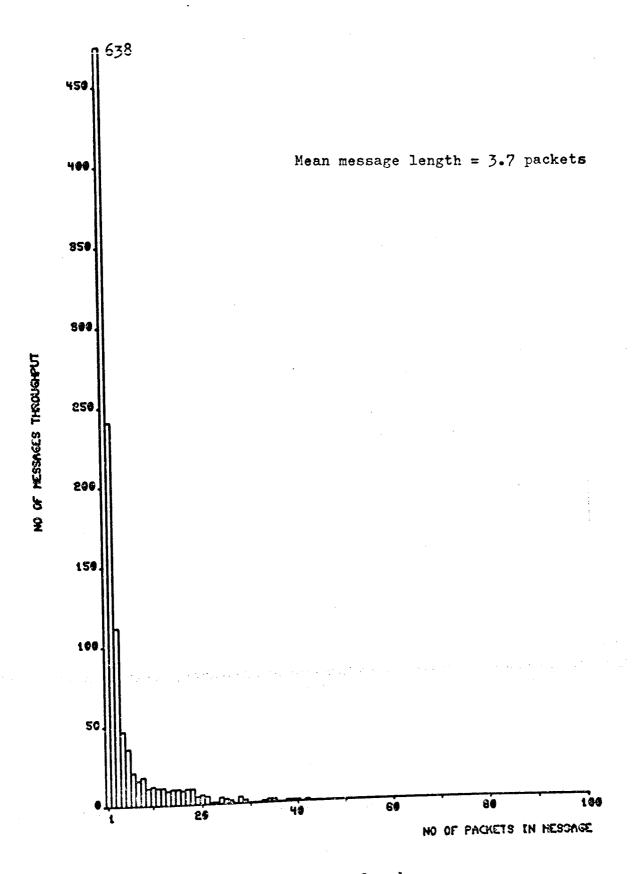

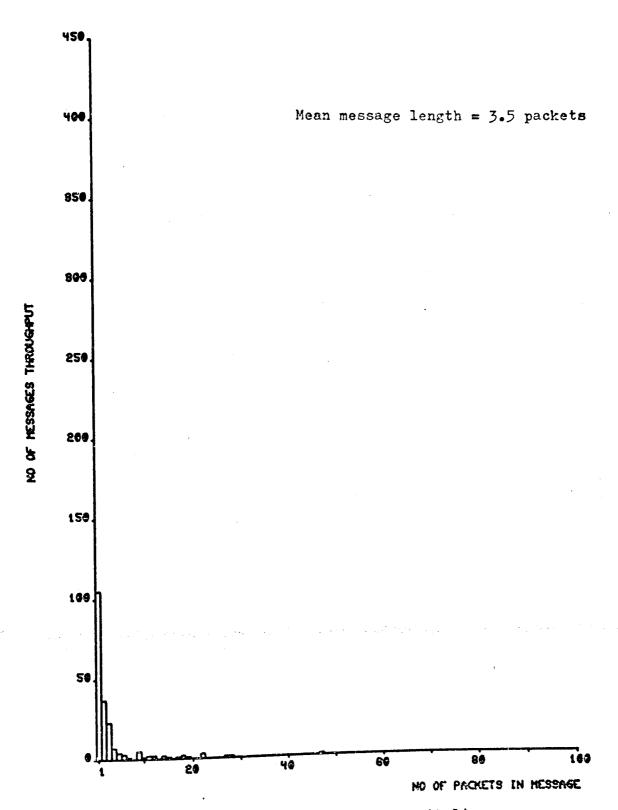

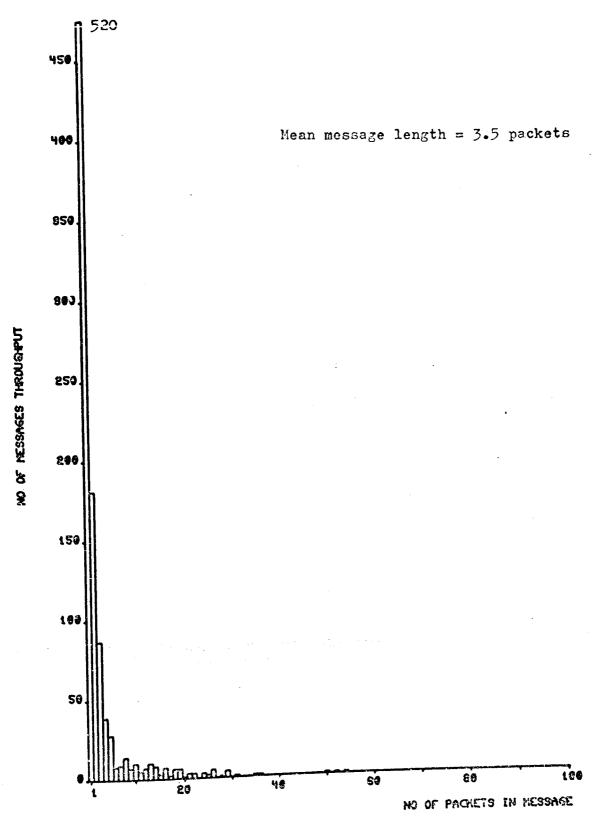

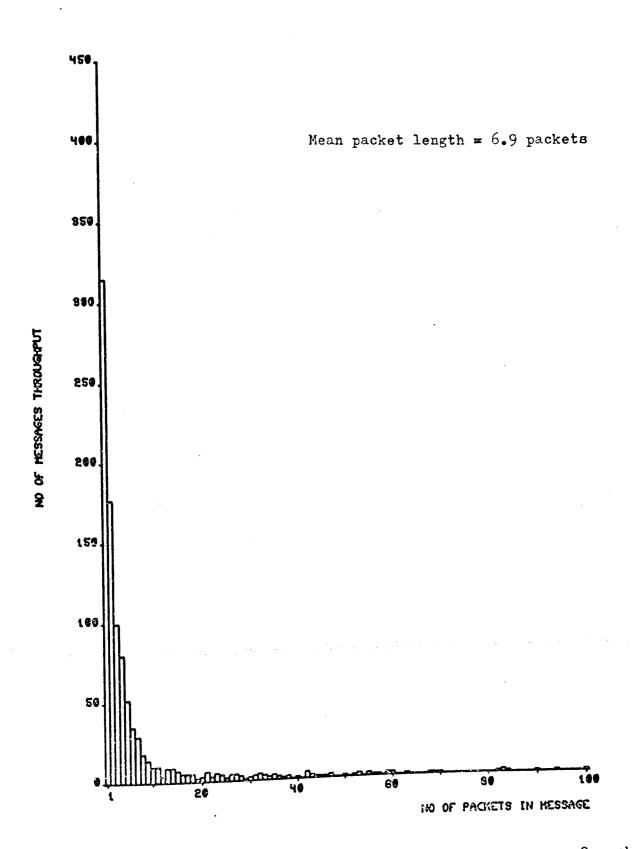

| 5.11         | Distribution of message lengths sent through network                                     | 132         |

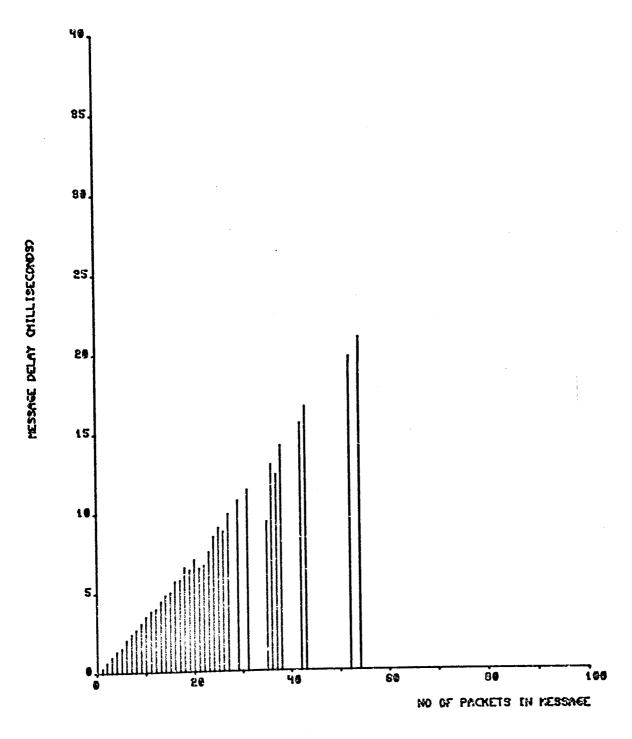

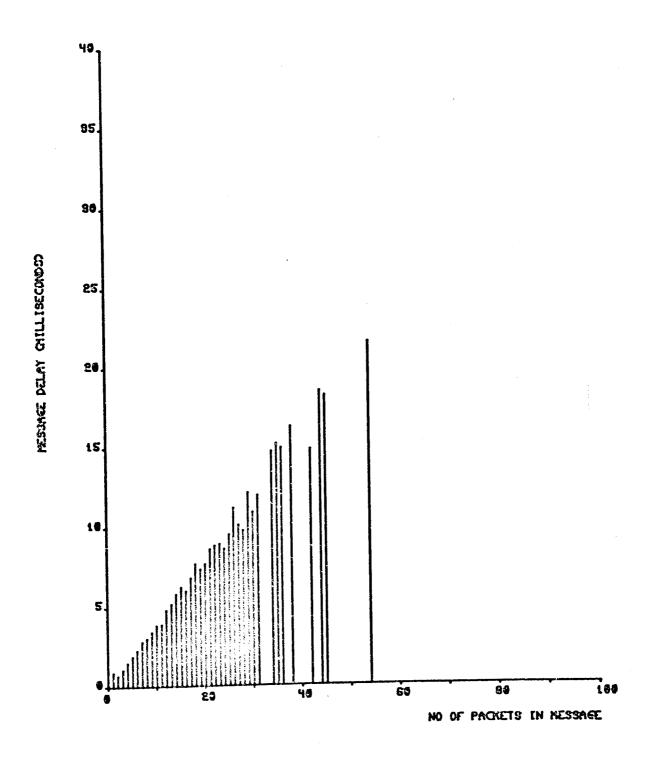

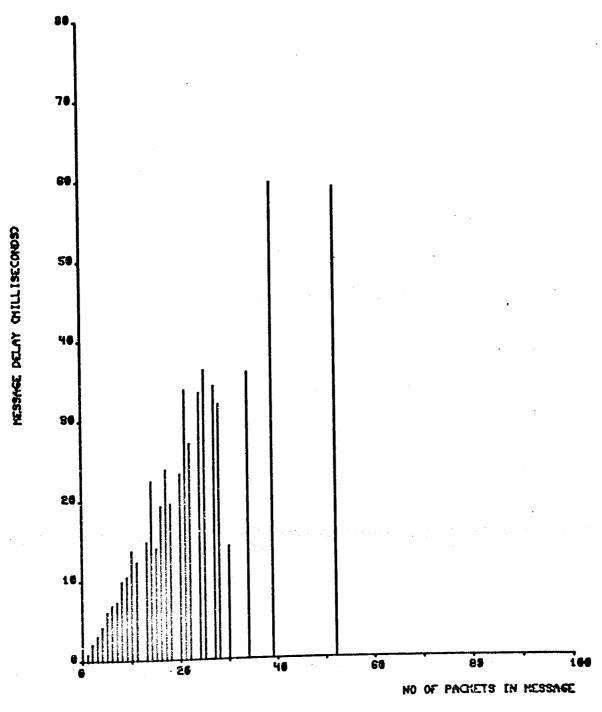

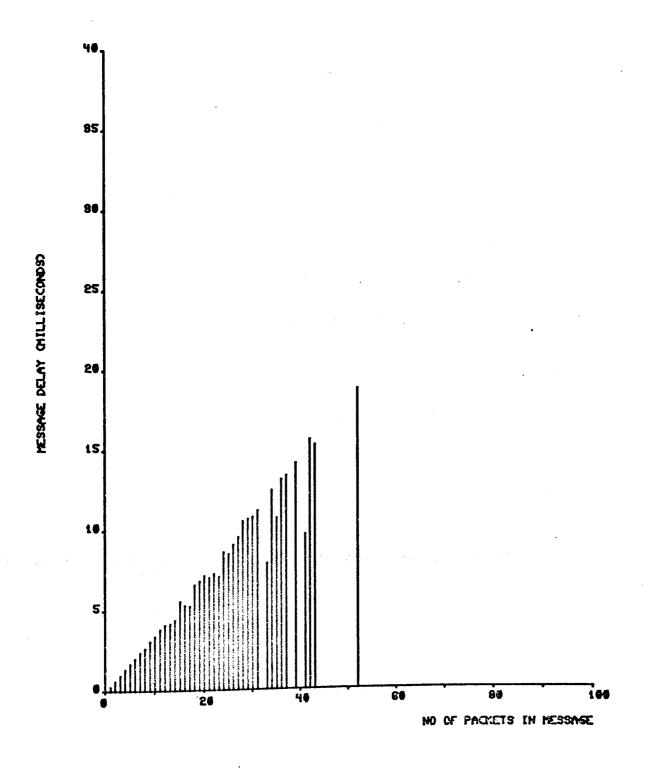

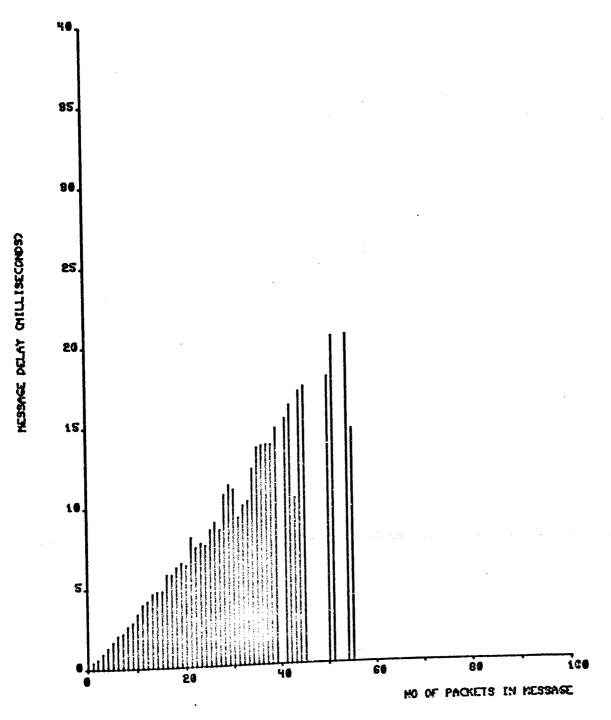

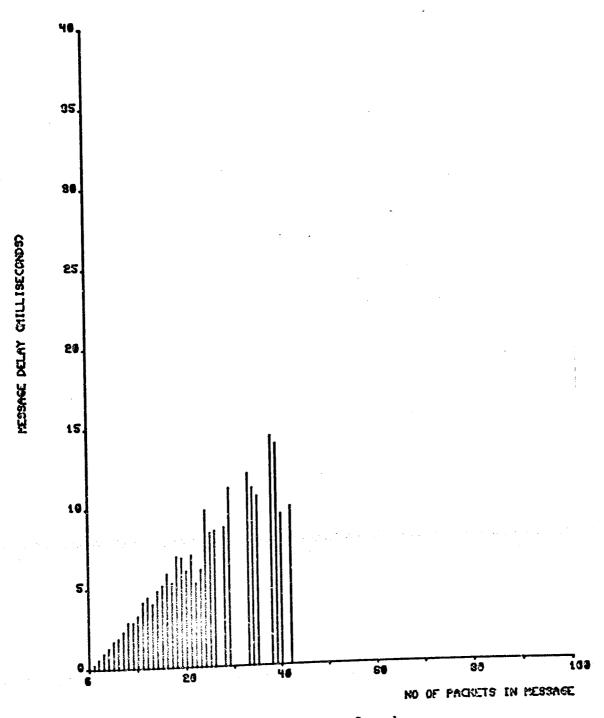

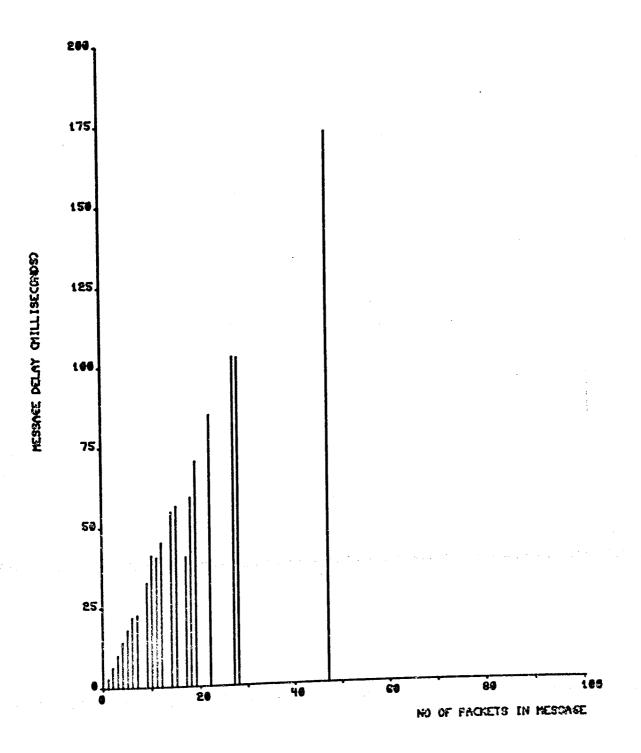

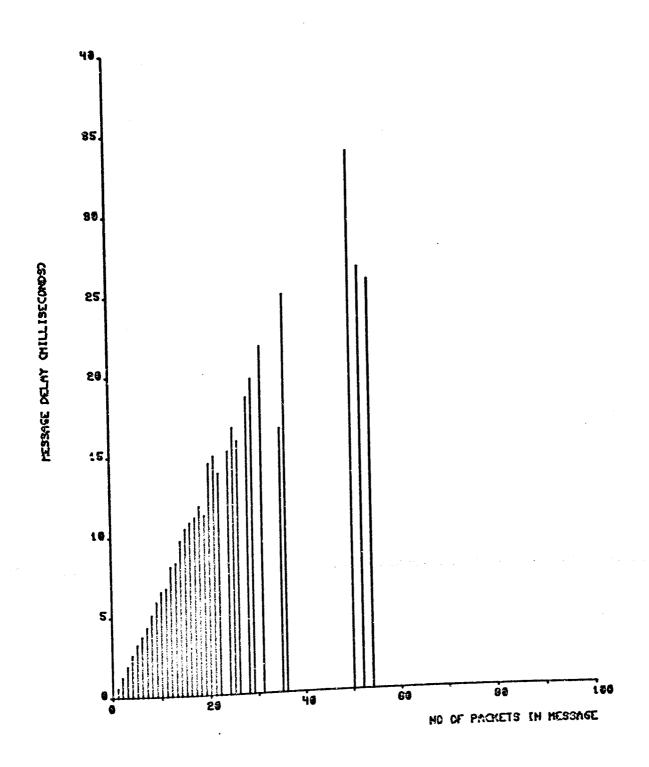

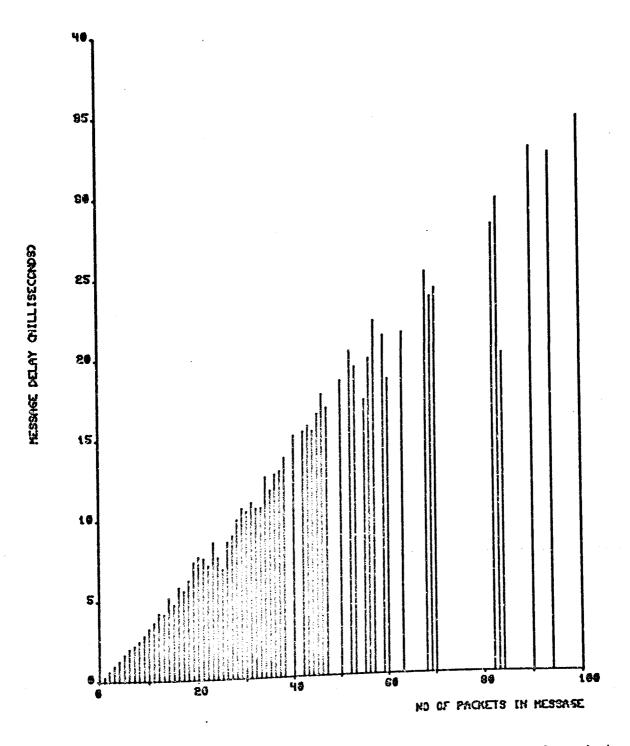

| 5.12         | Effect of message length on message throughput time                                      | 133         |

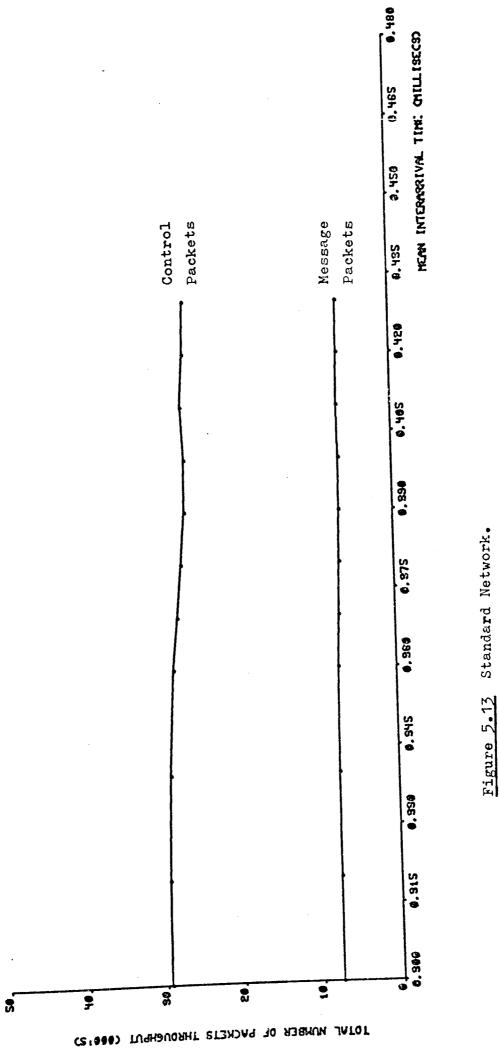

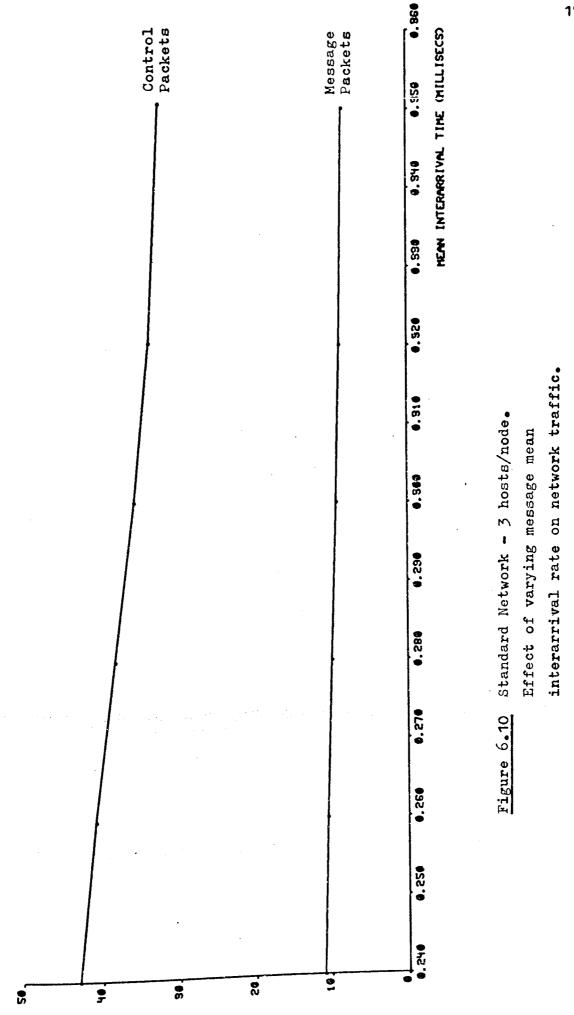

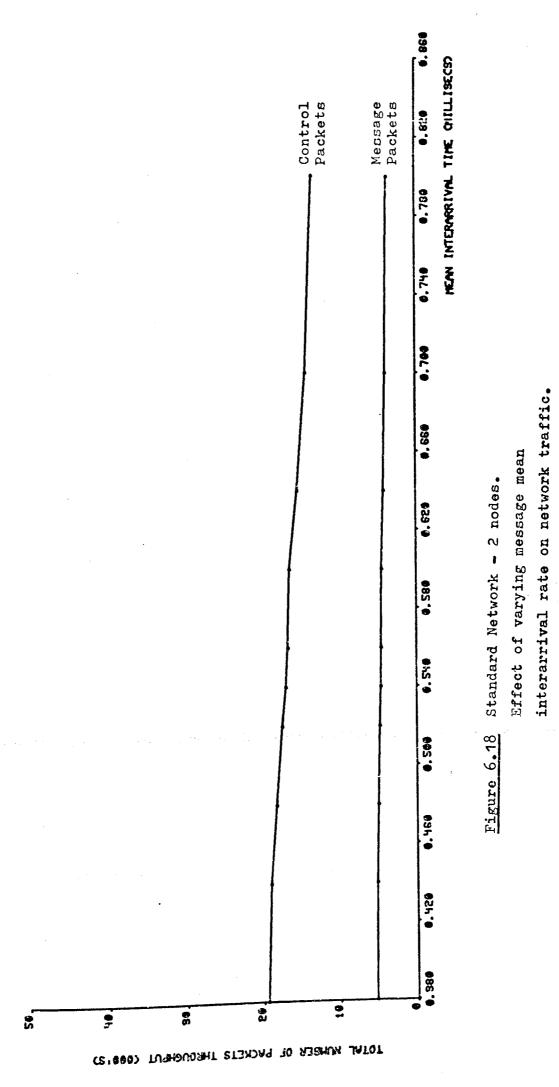

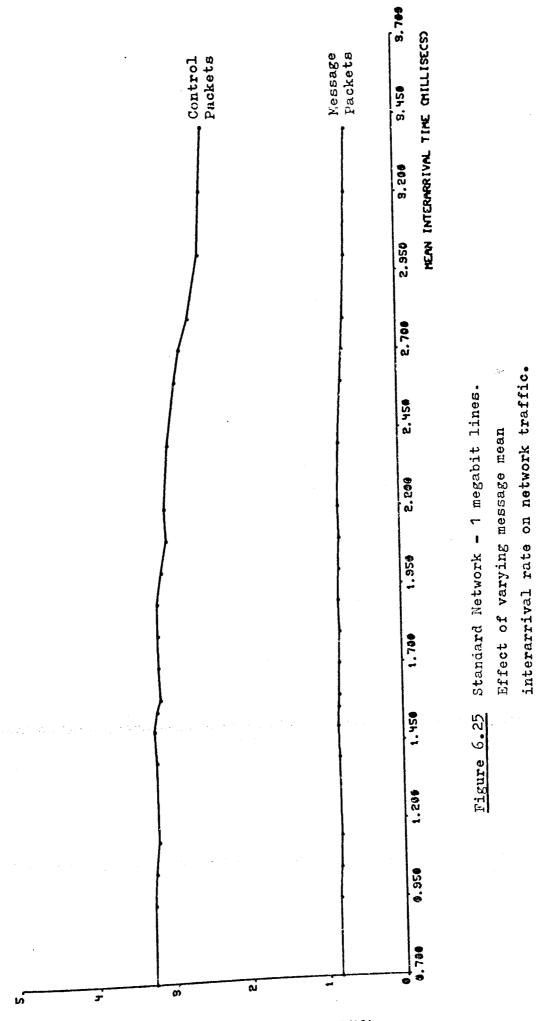

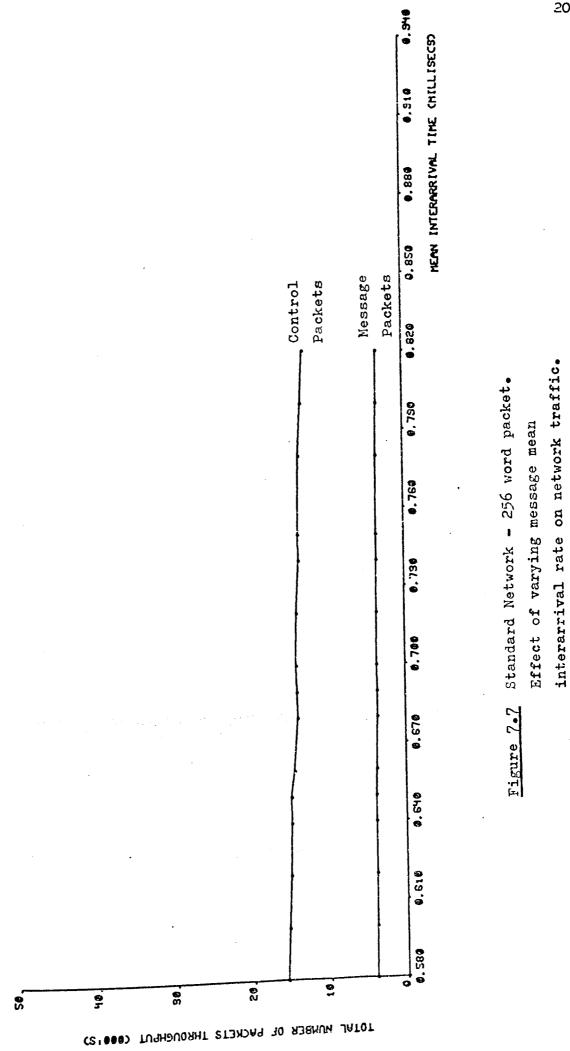

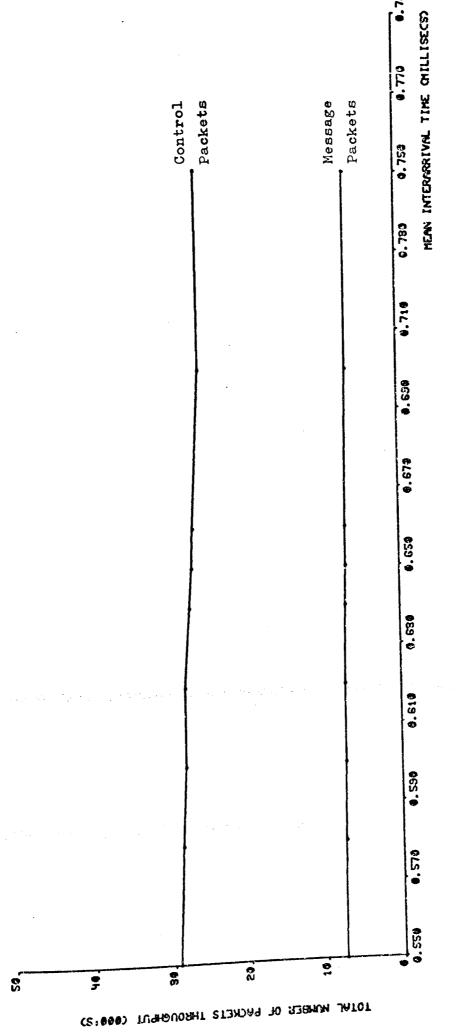

| <b>5.1</b> 3 | Effect of varying message mean interarrival rate on network traffic                      | 134         |

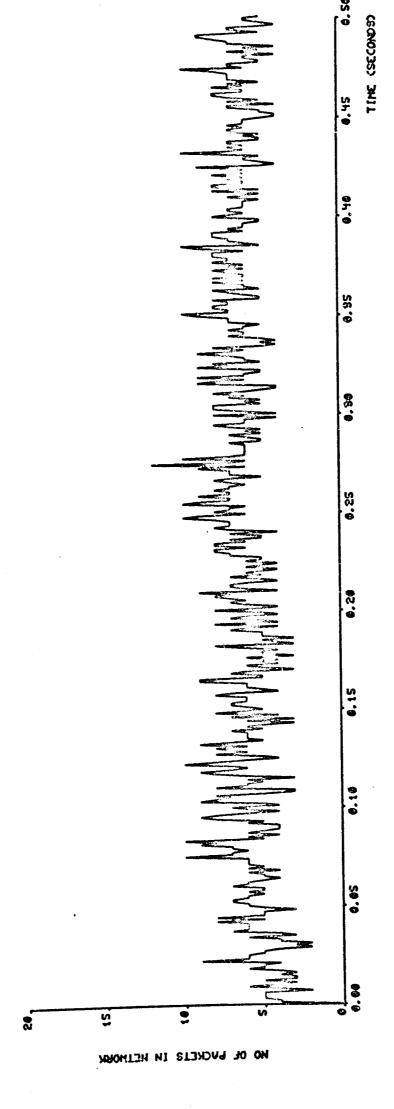

| 5.14         | Number of packets in network                                                             | 135         |

|              | Standard Network - 1 processor, 2 memory units per node                                  |             |

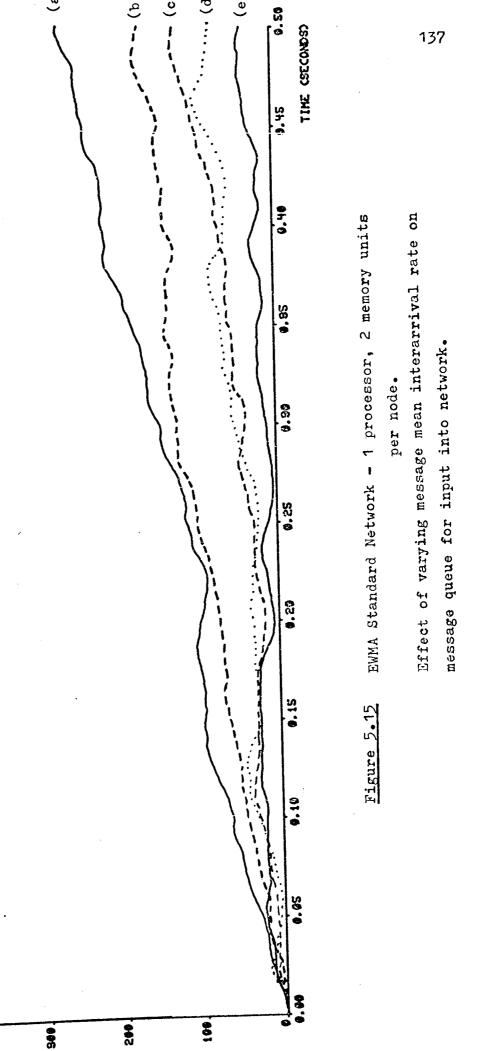

| 5•15         | Effect of varying message mean interarrival rate on message queue for input into network | 137         |

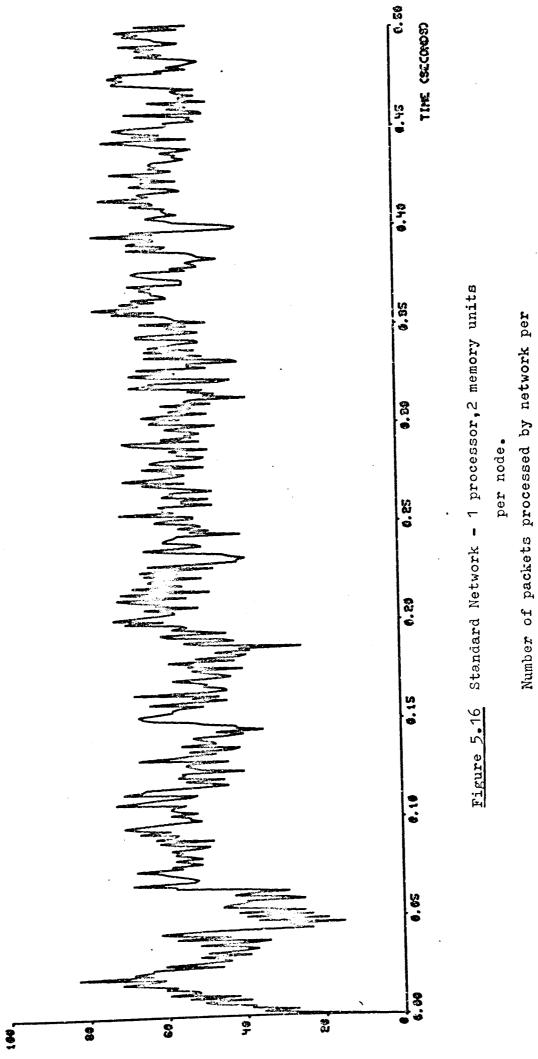

| 5.16         | Number of packets processed by network per millisecond sample interval                   | 138         |

| 5.17         | Percentage of network processor time used per millisecond sample interval                | 139         |

| 5.18         | Percentage of network memory time used per millisecond sample interval                   | 140         |

| 5•19         | Distribution of message lengths sent through network                                     | 141         |

| 5.20         | Effect of message lengths on message throughput time                                     | 142         |

| 5.21         | Effect of varying message mean interarrival rate on network traffic                      | 143         |

|              | Standard Network - 1 /4 second memory/processor                                          |             |

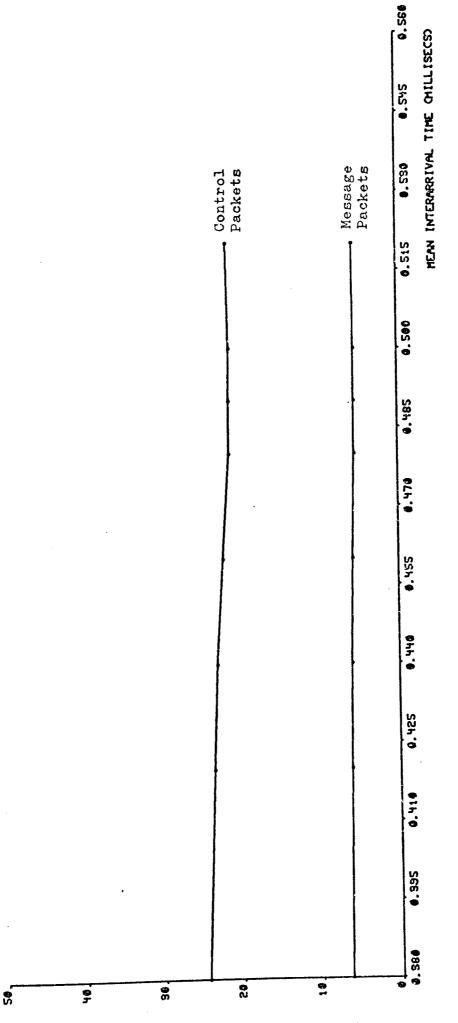

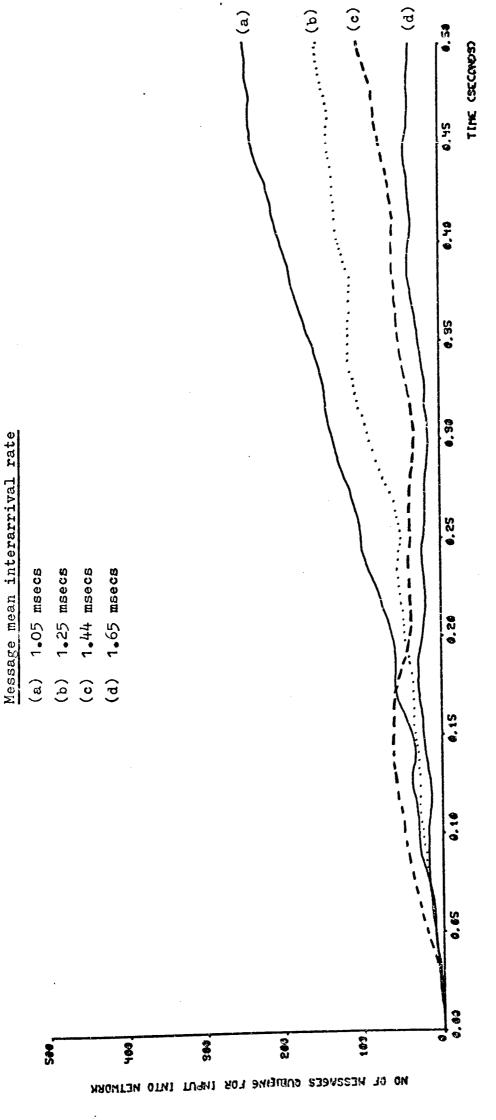

| 5.22         | Effect of varying message mean interarrival rate on message queue for input into network | <b>1</b> 46 |

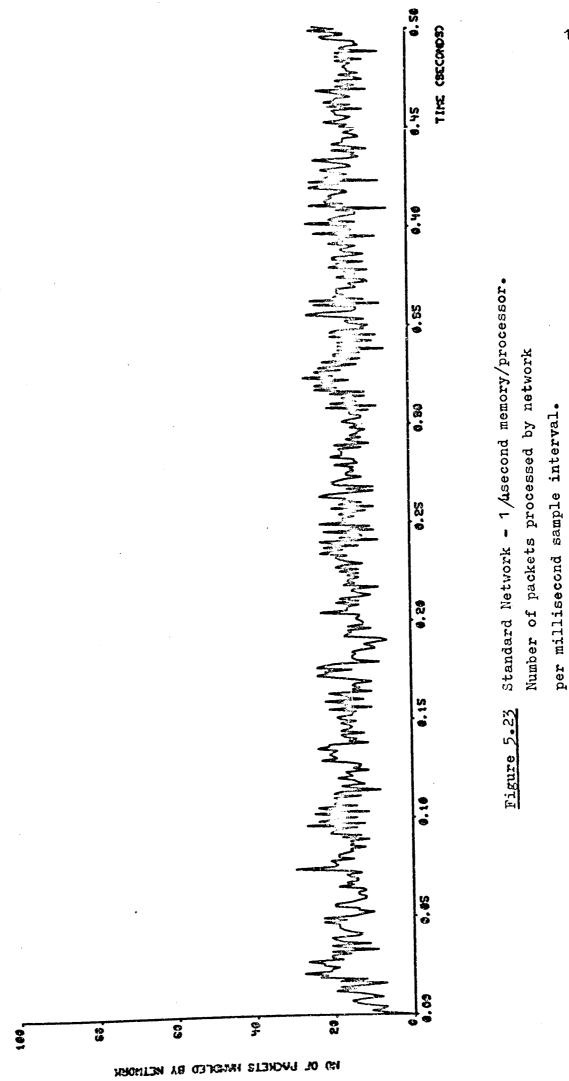

| 5•23         | Number of packets processed by network per millisecond sample interval                   | 147         |

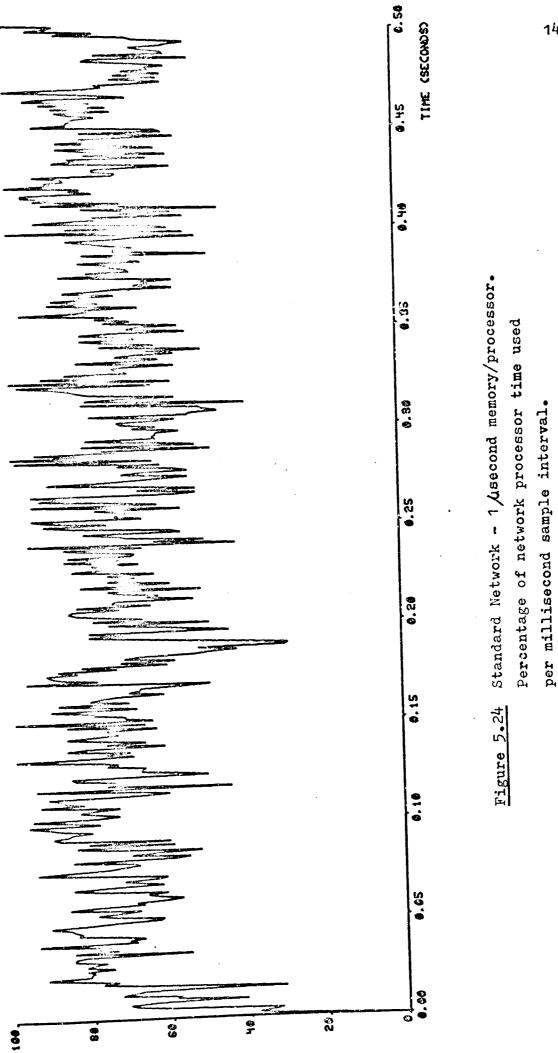

| 5.24         | Percentage of network processor time used per millisecond sample interval                | 148         |

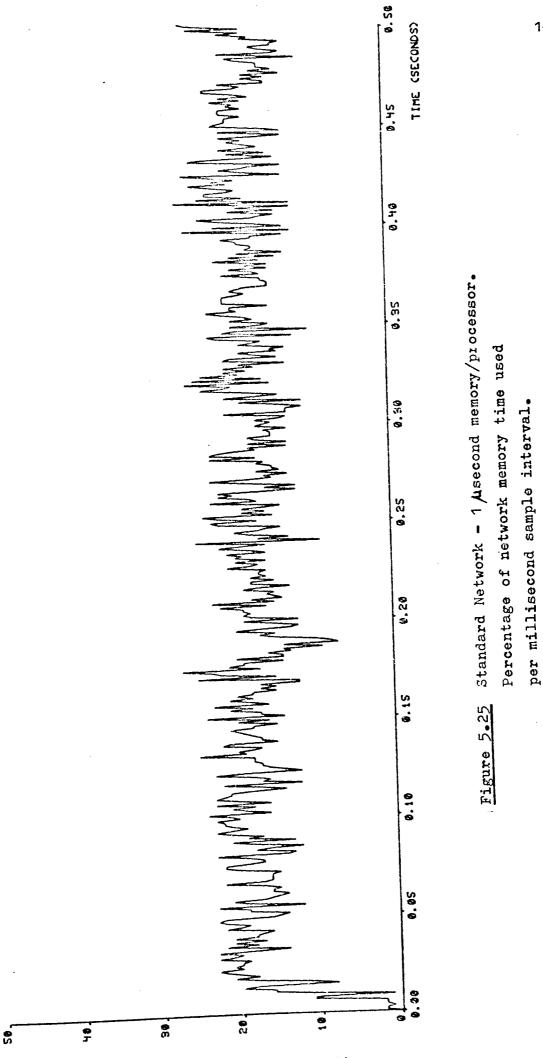

| 5•25         | Percentage of network memory time used per millisecond sample interval                   | 149         |

| 5.26         | Distribution of message lengths sent through network                                     | 150         |

| 5.27 | Effect of message length on message throughput time                                      | 151         |

|------|------------------------------------------------------------------------------------------|-------------|

| 5.28 | Effect of varying message mean interarrival rate on network traffic                      | 152         |

|      | Standard Network - 128 word memory module                                                |             |

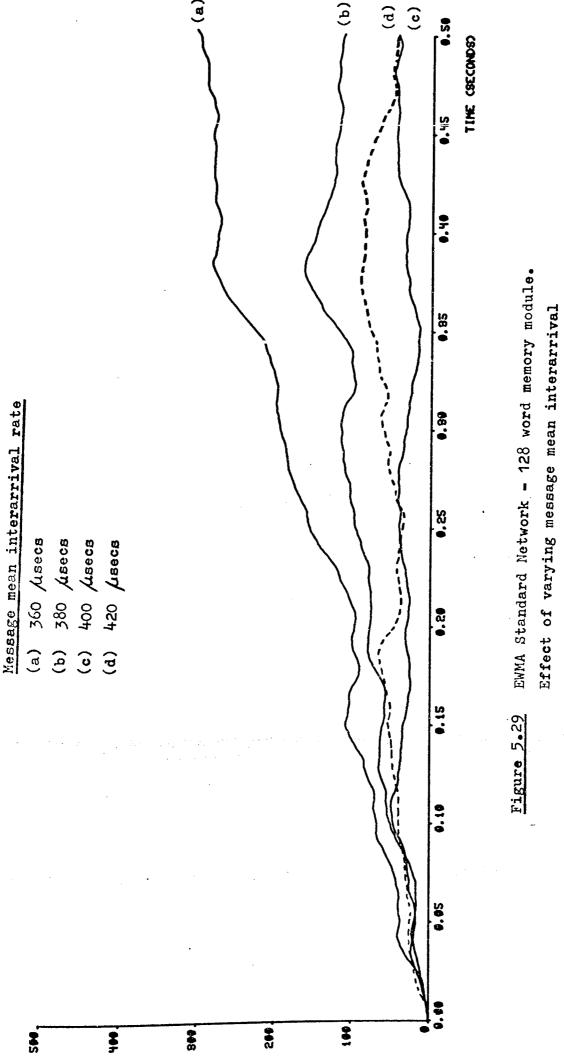

| 5•29 | Effect of varying message mean interarrival rate on message queue for input into network | 154         |

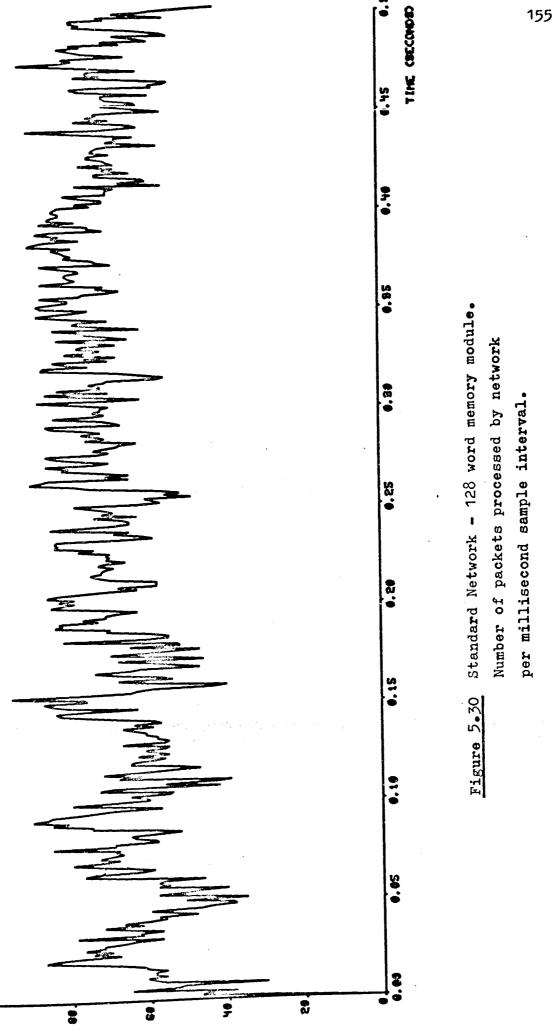

| 5•30 | Number of packets processed by network per millisecond sample interval                   | 155         |

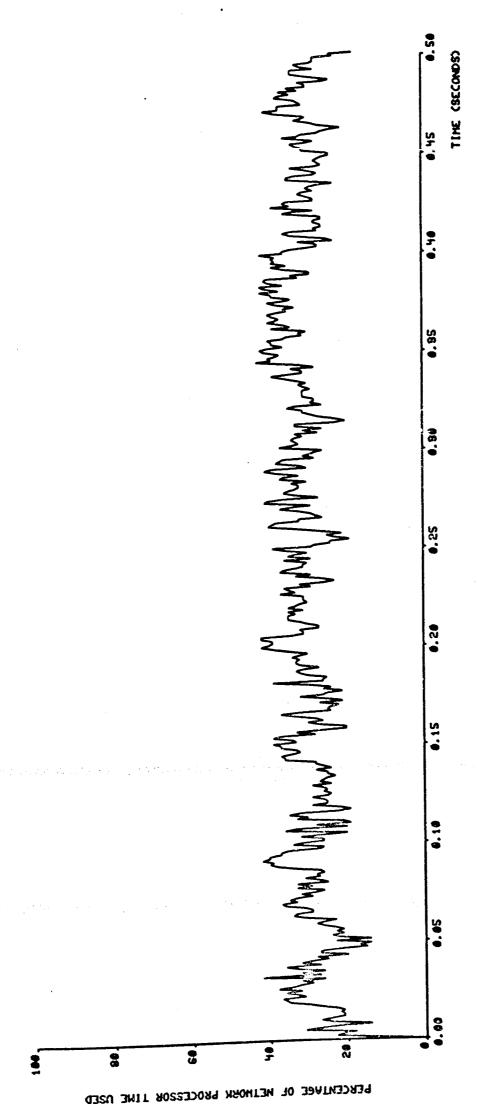

| 5•31 | Percentage of network processor time used per millisecond sample interval                | 156         |

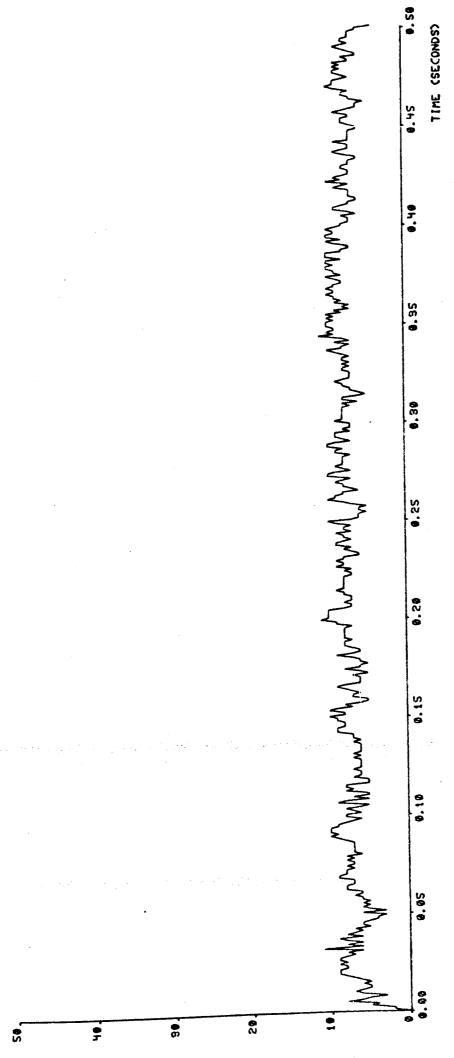

| 5•32 | Percentage of network memory time used per millisecond sample interval                   | 157         |

| 5•33 | Distribution of message lengths sent through network                                     | 158         |

| 5•34 | Effect of message length on message throughput time                                      | 159         |

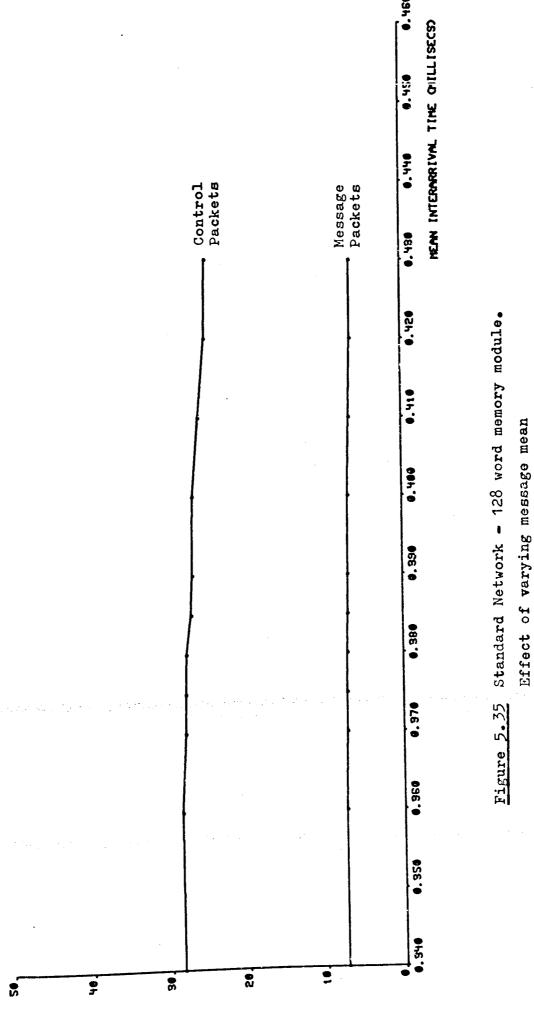

| 5•35 | Effect of varying message mean interarrival rate on network traffic                      | <b>1</b> 60 |

| 6.1  | Simple buffer lockup                                                                     | 162         |

| 6.2  | Double buffering                                                                         | <b>1</b> 63 |

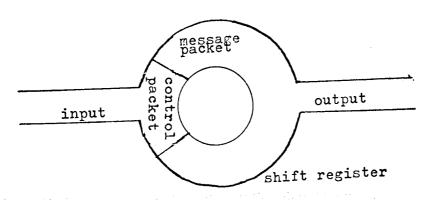

| 6.3  | Circular shift register capable of storing message and control packet                    | <b>1</b> 64 |

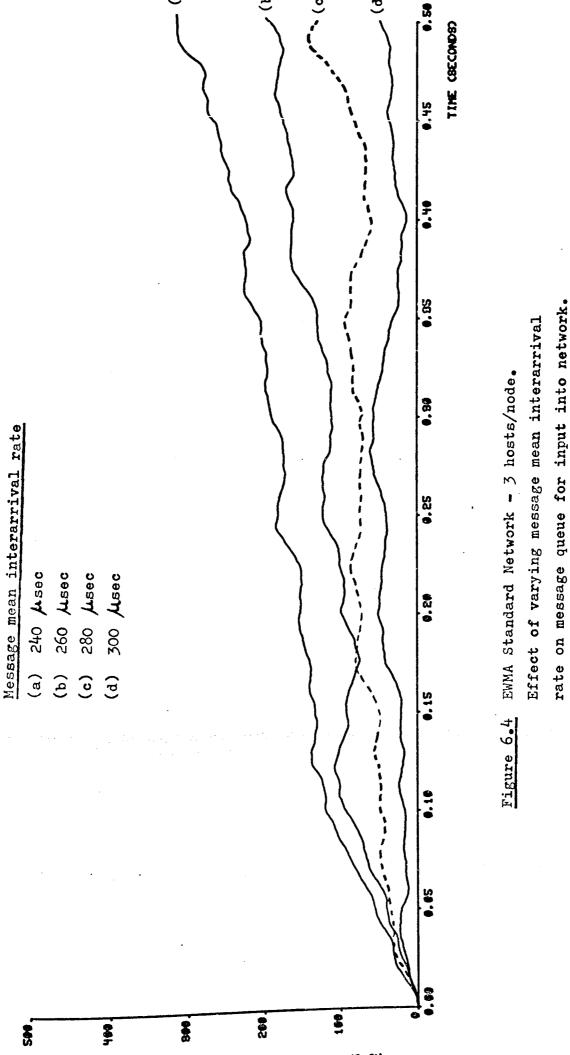

|      | Standard Network - 3 hosts/node                                                          |             |

| 6.4  | Effect of varying message mean interarrival rate on message queue for input into network | <b>1</b> 66 |

| 6.5  | Number of packets processed by network per millisecond sample interval                   | 167         |

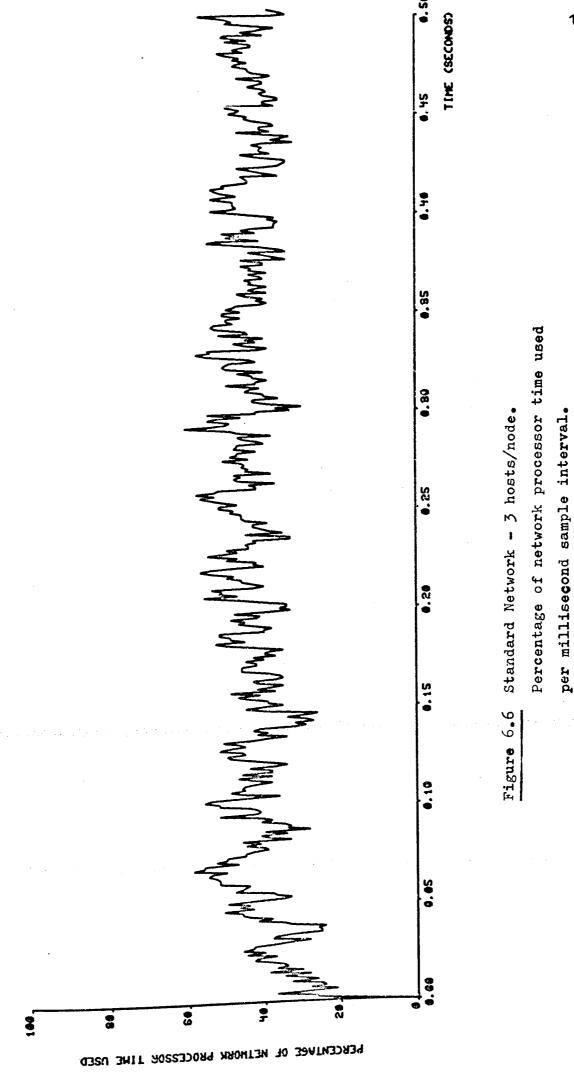

| 6.6  | Percentage of network processor time used per millisecond sample interval                | 168         |

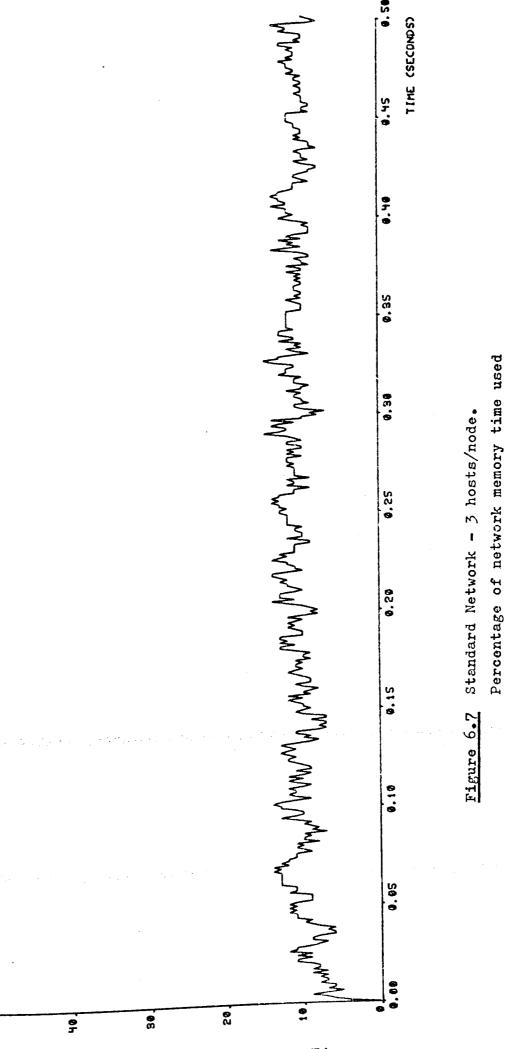

| 6.7  | Percentage of network memory time used per millisecond sample interval                   | 169         |

| 6.8  | Distribution of message lengths sent through network                                     | <b>1</b> 70 |

| 6.9  | Effect of message length on message throughput time                                      | 171         |

| 6.10 | Effect of varying message mean interarrival rate on network traffic                      | 172         |

| , |      |                                                                                          |             |

|---|------|------------------------------------------------------------------------------------------|-------------|

|   | 6.11 | Number of paths transversed during a typical host/host transaction                       | 174         |

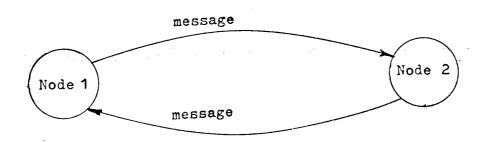

|   |      | Standard Network - 2 nodes                                                               |             |

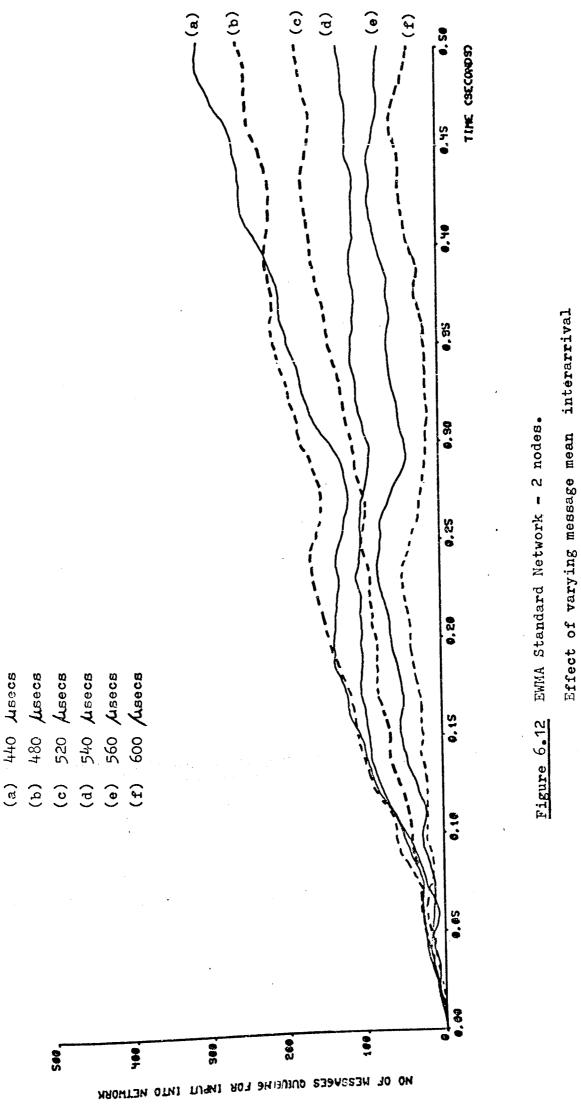

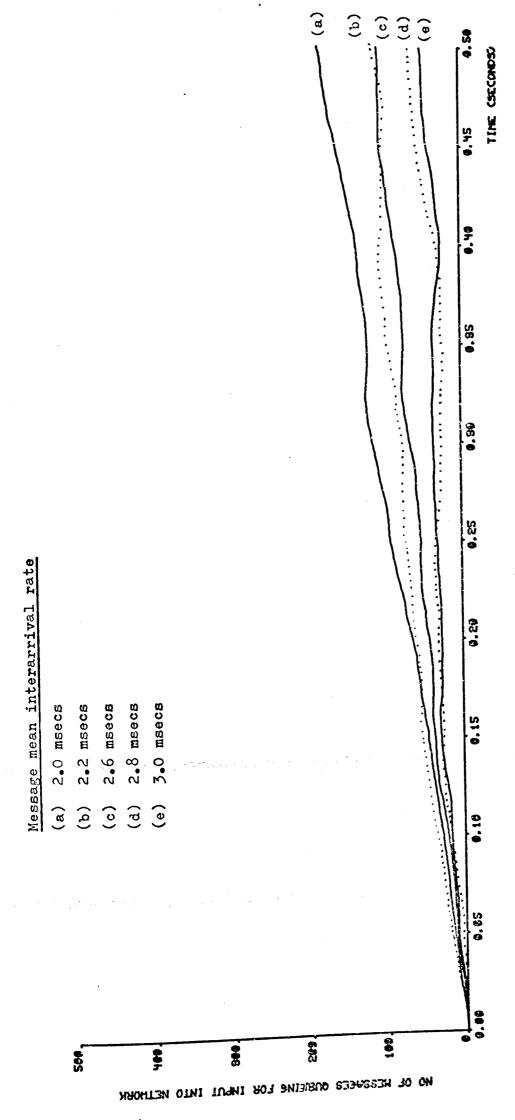

|   | 6.12 | Effect of varying message mean interarrival rate on message queue for input into network | 175         |

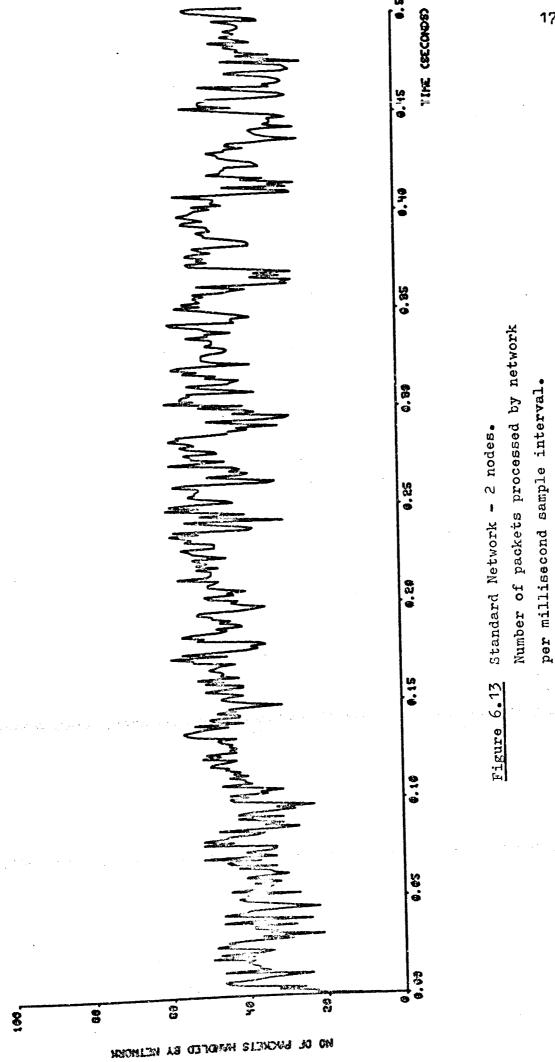

|   | 6.13 | Number of packets processed by network per millisecond sample interval                   | 176         |

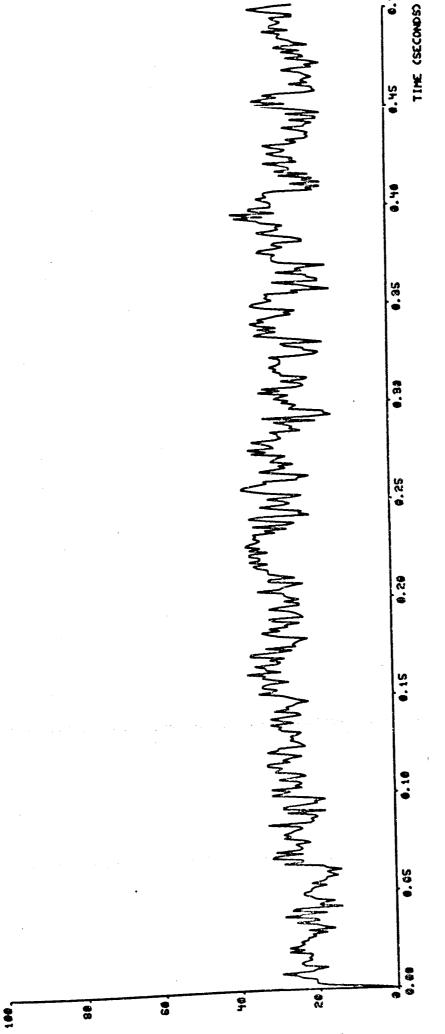

|   | 6.14 | Percentage of network processor time used per millisecond sample interval                | 177         |

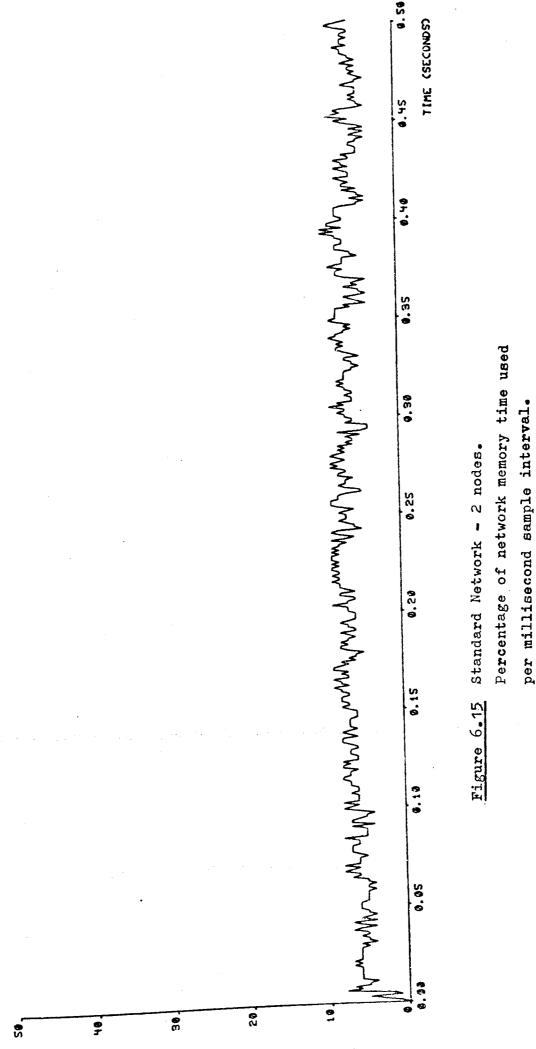

|   | 6.15 | Percentage of network memory time used per millisecond sample interval                   | 178         |

|   | 6.16 | Distribution of message lengths sent through network                                     | 179         |

|   | 6.17 | Effect of message length on message throughput time                                      | 180         |

|   | 6.18 | Effect of varying message mean interarrival rate on network traffic                      | 181         |

|   |      | Standard Network - 1 megabit lines                                                       |             |

|   | 6.19 | Effect of varying message mean interarrival rate on message queue for input into network | 183         |

|   | 6.20 | Number of packets processed by network per millisecond sample interval                   | 184         |

|   | 6.21 | Percentage of network processor time used per millisecond sample interval                | <b>1</b> 85 |

|   | 6.22 | Percentage of network memory time used per millisecond sample interval                   | 186         |

|   | 6.23 | Distribution of message lengths sent through network                                     | 187         |

|   | 6.24 | Effect of message length on message throughput time                                      | <b>1</b> 88 |

|   | 6.25 | Effect of varying message mean interarrival rate on network traffic                      | 189         |

| - |      | Standard Network - 100k bit lines                                                        |             |

|   | 6.26 | Effect of varying message mean interarrival rate on message queue for input into network | 190         |

|   | 6.27 | Number of packets processed by network per millisecond sample interval                   | 191         |

|   |      |                                                                                          |             |

•

•

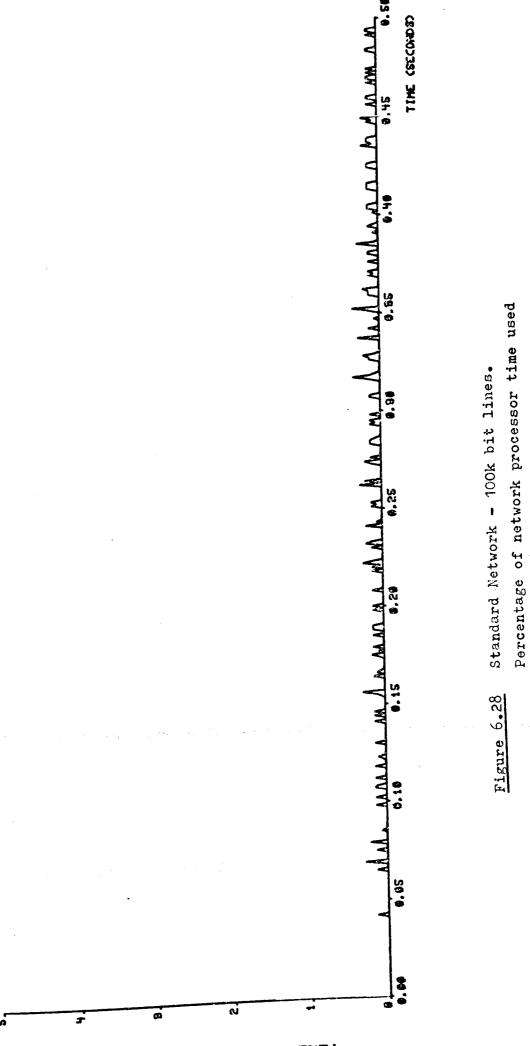

|   | 6.28 | Percentage of network processor time used per millisecond sample interval                | 192 |

|---|------|------------------------------------------------------------------------------------------|-----|

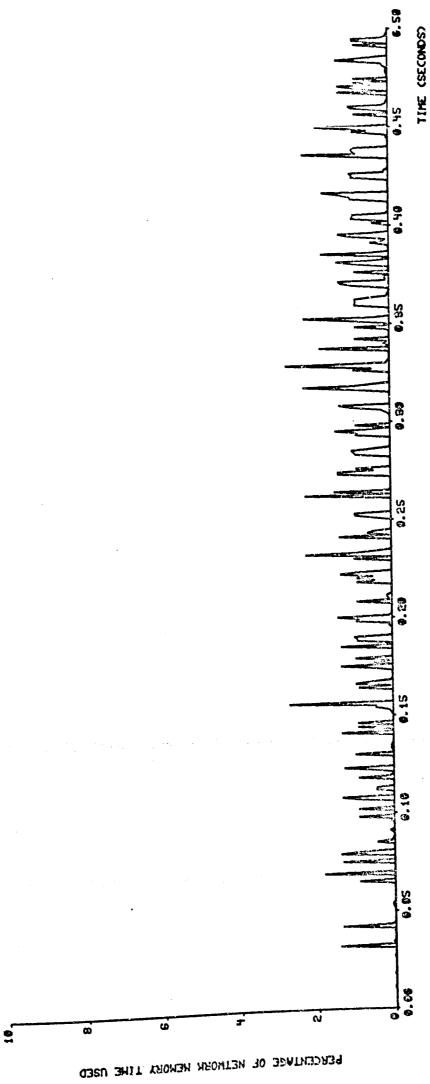

|   | 6.29 | Percentage of network memory time used per<br>millisecond sample interval                | 193 |

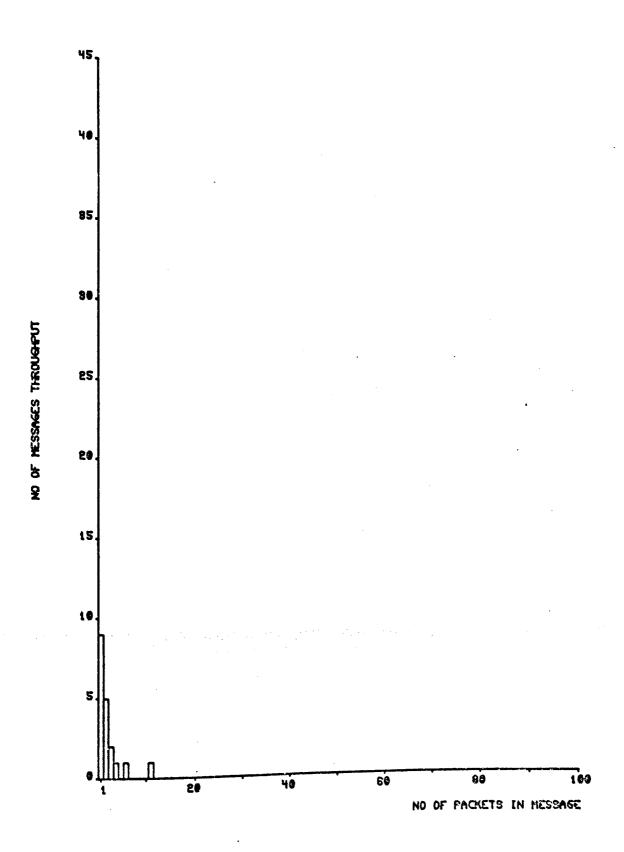

|   | 6.30 | Distribution of message length sent through network                                      | 194 |

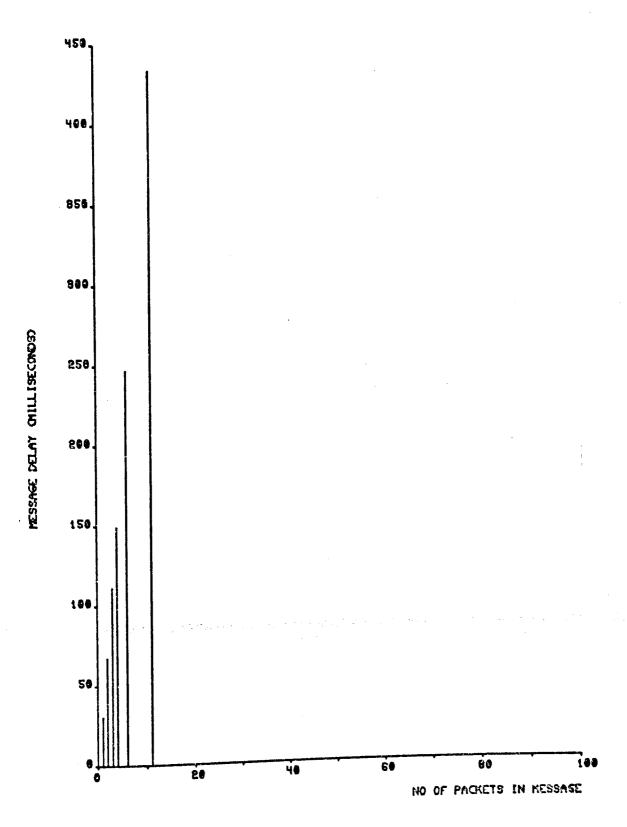

|   | 6.31 | Effect of message length on message throughput time                                      | 195 |

|   | 6.32 | Effect of varying message mean interarrival rate on network traffic                      | 196 |

|   |      | Standard Network - 256 word packet                                                       |     |

|   | 7.1  | Effect of varying message mean interarrival rate on message queue for input into network | 198 |

|   | 7.2  | Number of packets processed by network per millisecond sample interval                   | 199 |

|   | 7.•3 | Percentage of network processor time used per millisecond sample interval                | 200 |

|   | 7.4  | Percentage of network memory time used per millisecond sample interval                   | 201 |

|   | 7•5  | Distribution of message length sent through network                                      | 202 |

|   | 7.6  | Effect of message length on message throughput time                                      | 203 |

|   | 7•7  | Effect of varying message mean interarrival rate on network traffic                      | 204 |

|   |      | Standard Network - mean short message = 2 packets - mean long message = 20 packets       |     |

|   | 7.8  | Effect of varying message mean interarrival rate on message queue for input into network | 206 |

|   | 7•9  | Number of packets processed by network per millisecond interval                          | 207 |

| · | 7.10 | Percentage of network processor time used per millisecond sample interval                | 208 |

|   | 7.11 | Percentage of network memory time used per millisecond sample interval                   | 209 |

|   | 7.12 | Distribution of message lengths sent through network                                     | 210 |

|   | 7.13 | Effect of message length on message throughput time                                      | 211 |

|   | 7.14 | Effect of varying message mean interarrival rate on network traffic                      | 212         |

|---|------|------------------------------------------------------------------------------------------|-------------|

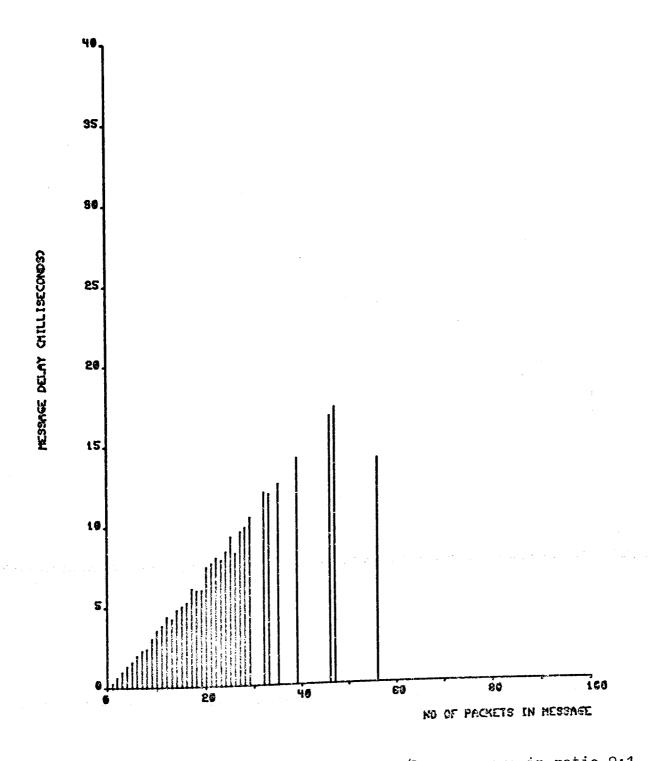

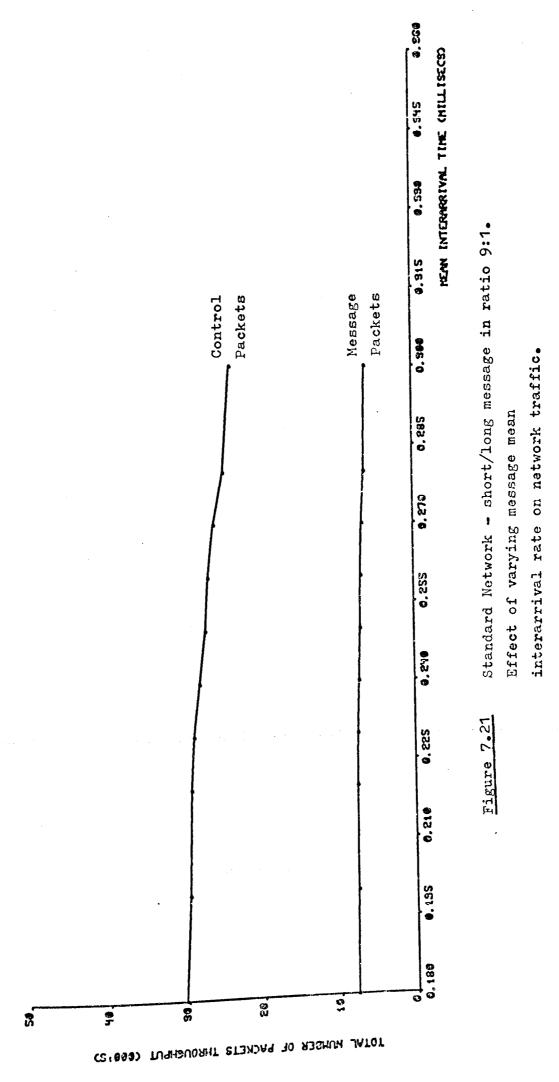

|   |      | Standard Network - short/long message in ratio 9:1                                       |             |

|   | 7•15 | Effect of varying message mean interarrival rate on message queue for input into network | 214         |

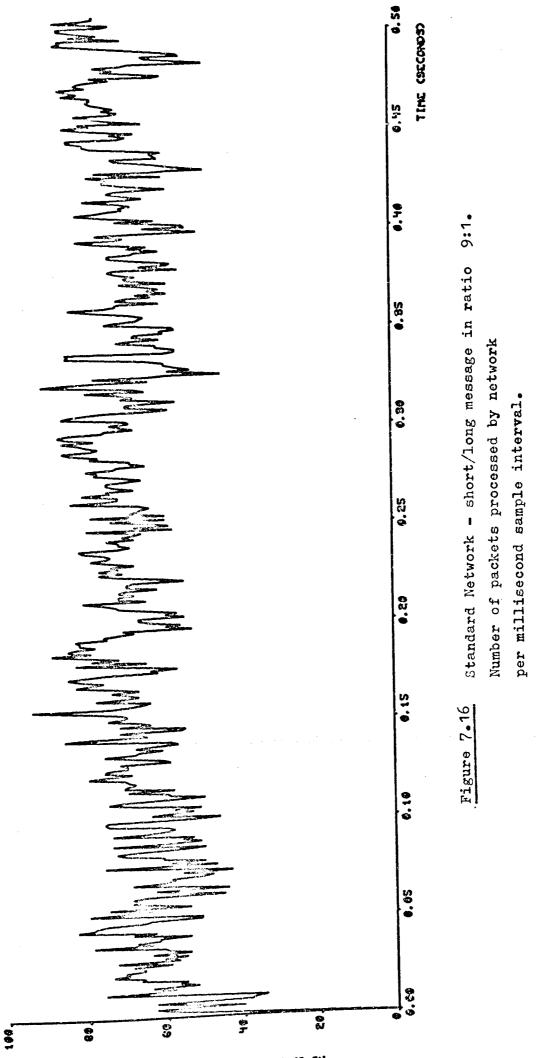

|   | 7.16 | Number of packets processed by network per millisecond sample interval                   | 215         |

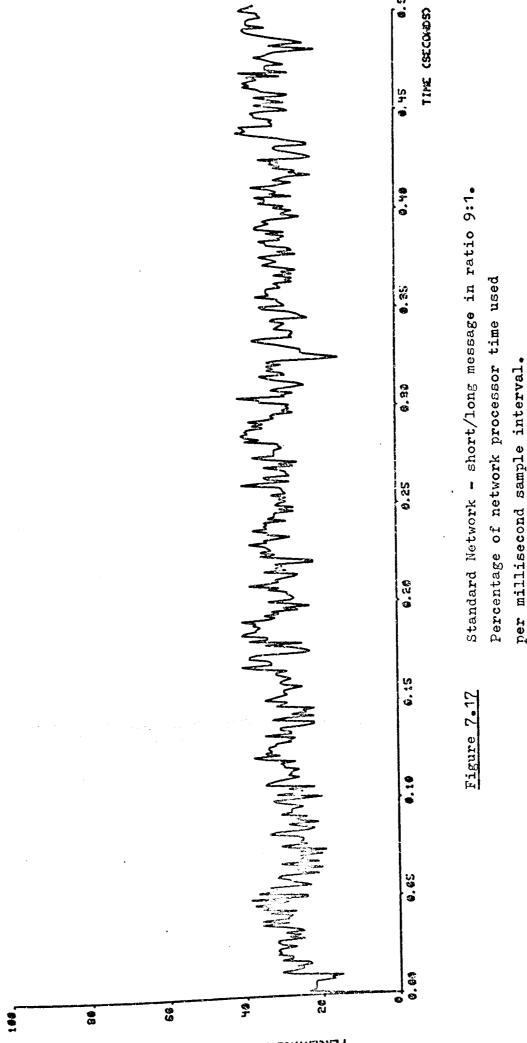

|   | 7.17 | Percentage of network processor time used per millisecond sample interval                | 216         |

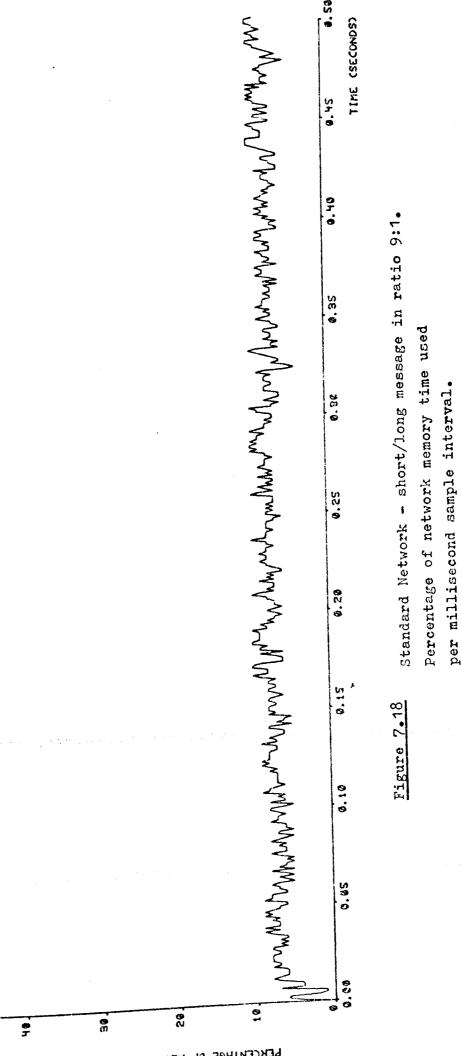

|   | 7.18 | Percentage of network memory time used per millisecond sample interval                   | 217         |

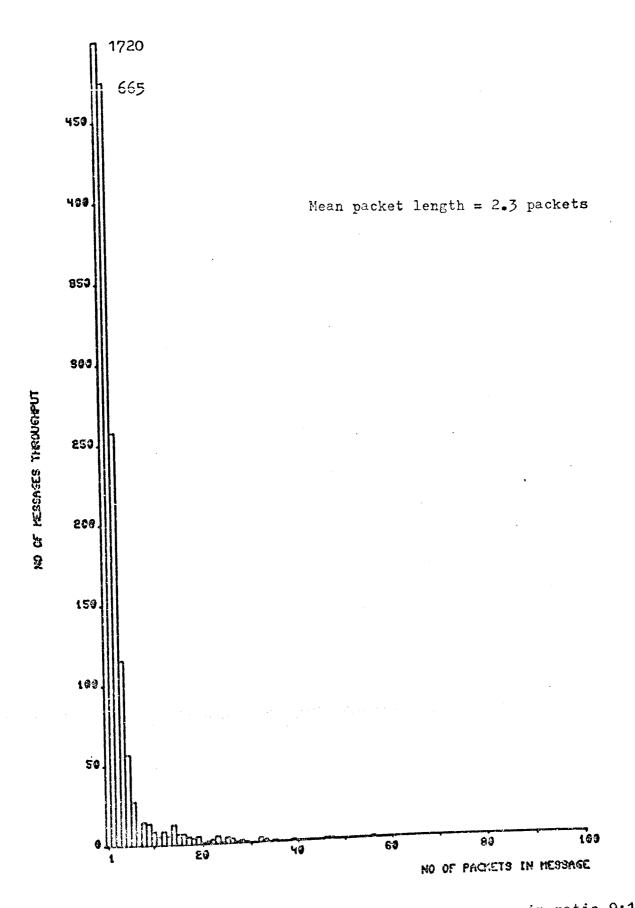

|   | 7.19 | Distribution of message lengths sent through network                                     | 218 .       |

| , | 7.20 | Effect of message length on message throughput time                                      | 219         |

|   | 7.21 | Effect of varying message mean interarrival rate on network traffic                      | 220         |

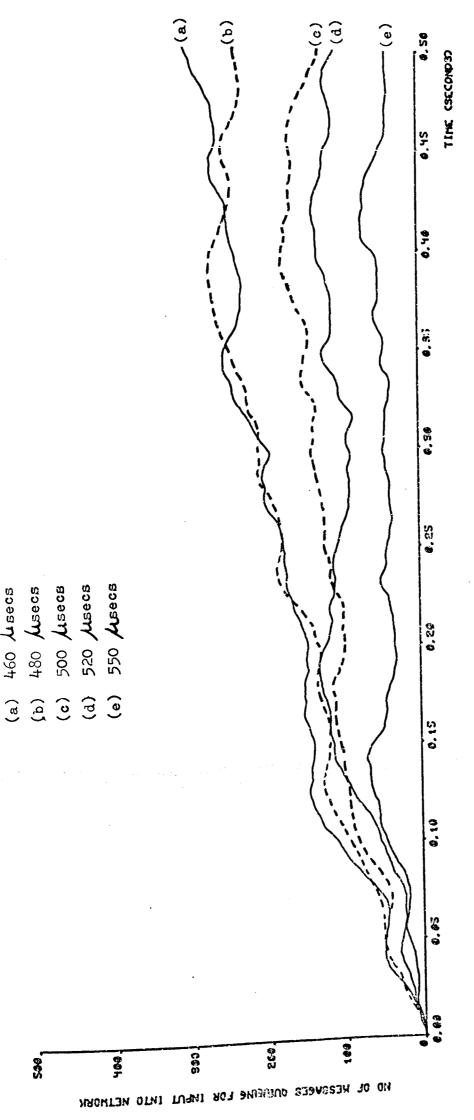

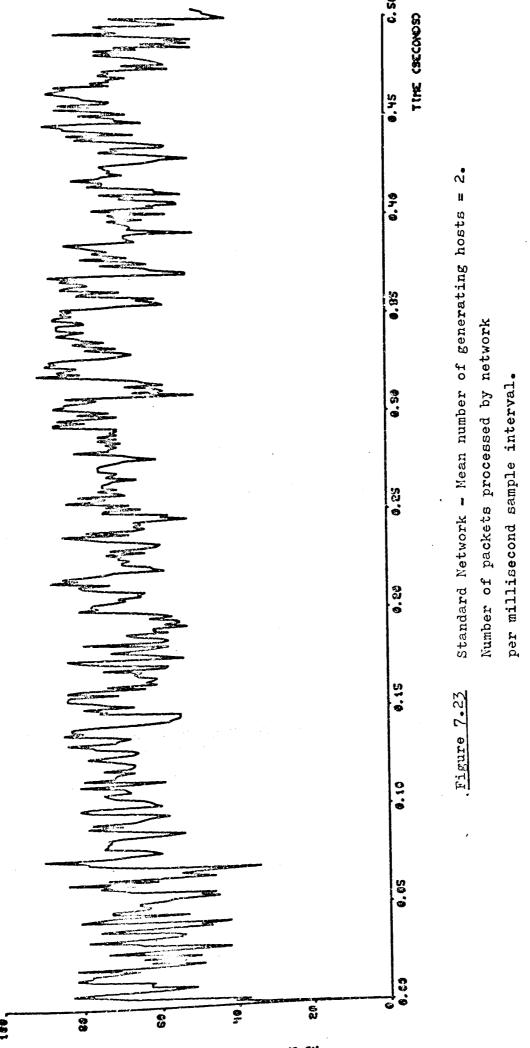

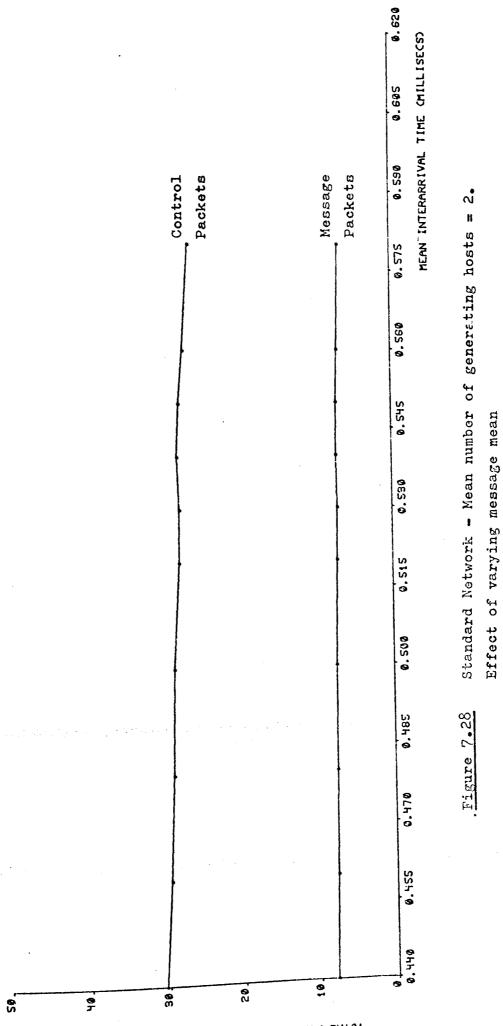

|   |      | Standard Network - Mean number of generating hosts =                                     | <u>2</u>    |

|   | 7.22 | Effect of varying message mean interarrival rate on message queue for input into network | 222         |

|   | 7.23 | Number of packets processed by network per millisecond sample interval                   | 223         |

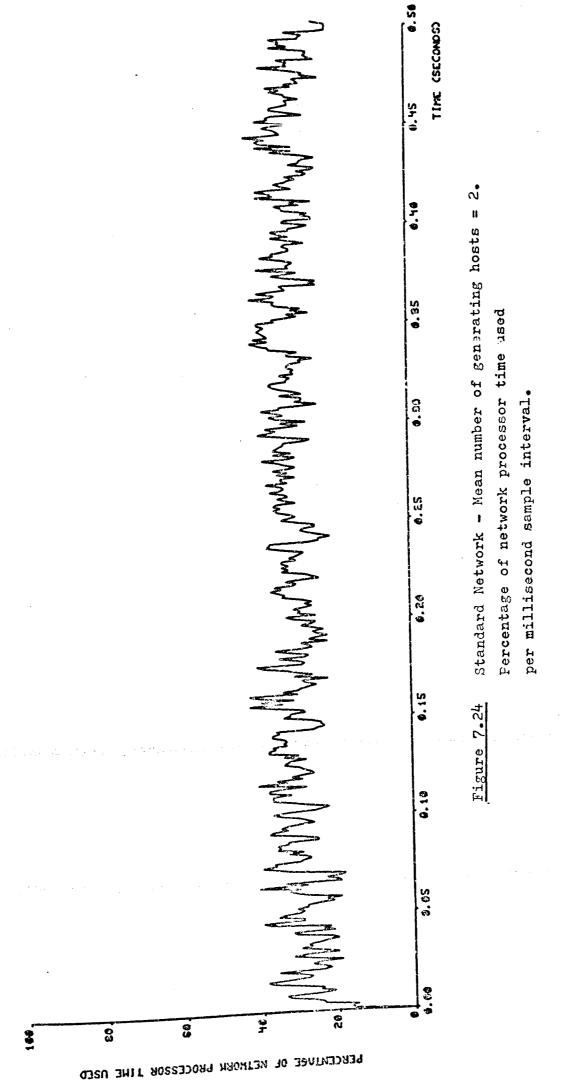

|   | 7.24 | Percentage of network processor time used per millisecond sample interval                | 224         |

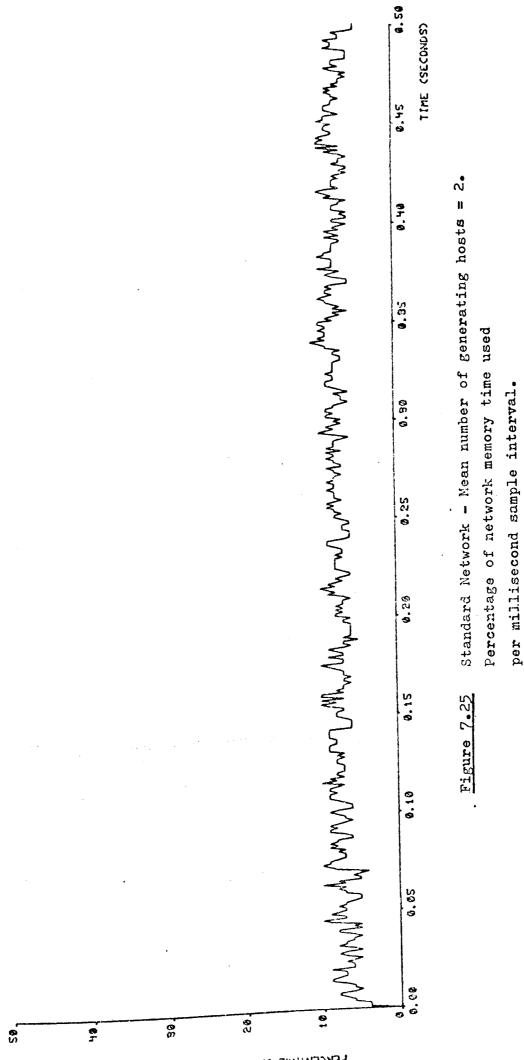

|   | 7.25 | Percentage of network memory time used per millisecond sample interval                   | 225         |

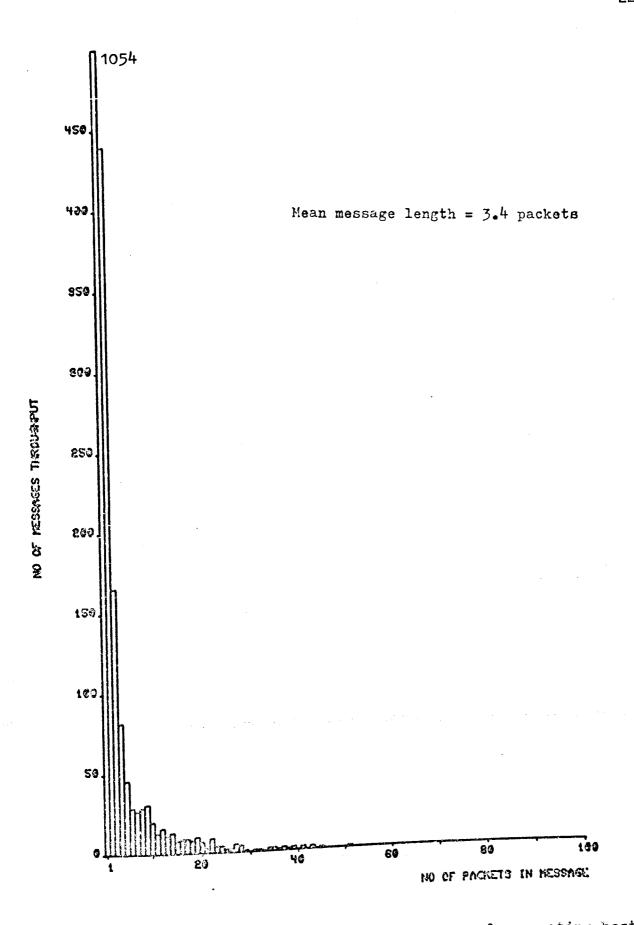

|   | 7.26 | Distribution of message lengths sent through network                                     | 226         |

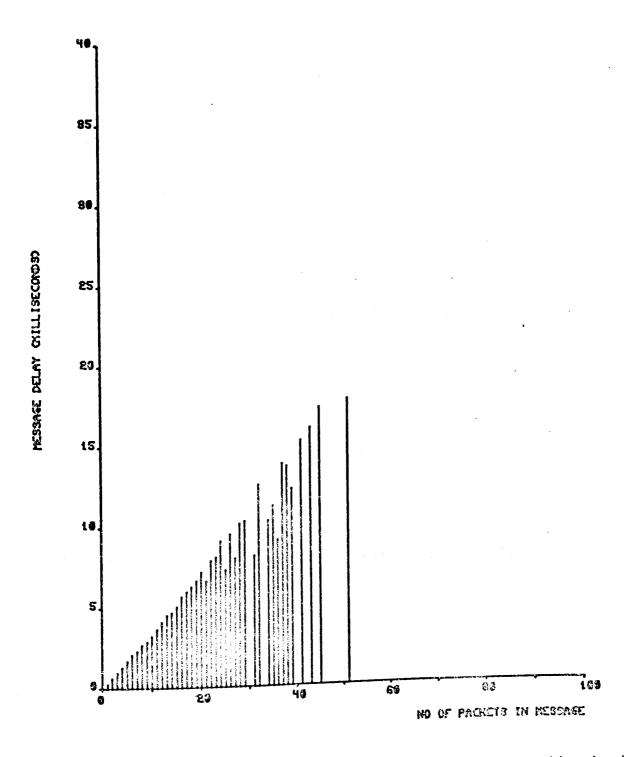

|   | 7.27 | Effect of message length on message throughput time                                      | 227         |

|   | 7.28 | Effect of varying message mean interarrival rate on network traffic                      | <b>2</b> 28 |

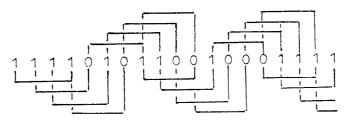

|   | I.1  | Unique sets of digits in sequence                                                        | 238         |

|   | 1.2  | Chaincode produced by four stage shift register                                          | 238         |

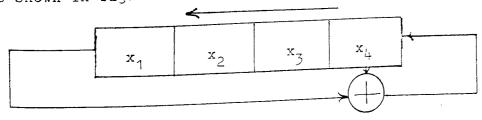

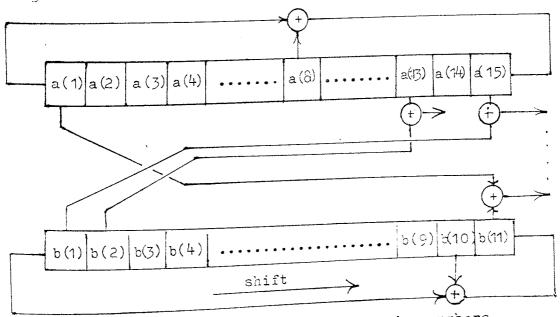

|   | 1.3  | Generation of pseudo-random numbers using two independent chaincodes                     | 239         |

#### CHAPTER ONE

#### INTRODUCTION TO COMPUTER NETWORKS

Computer networks are the product of the seventies and will undoubtedly take over from the time-sharing industry of the previous decade. Their effect on society and the economy will be more profound than any other network developed to date.

A computer network can be defined as "an interconnection of dependent or independent computer systems which communicate with each other in order to share certain resources such as programs and/or data; load sharing; and reliability reasons."

Functioning computer networks have been in existence for several years since the early sixties. They include CYBERNET, MERIT and OCTOPUS but perhaps the most sophisticated and ambitious computer network in existence is the ARPA network.

A network can be divided into two parts: one part consisting of the computers which provide the computational services of the network - the "HOSTS"; and the other part consisting of those computers which service the communication needs of the network - the "NODES."

Computer networks are set up as a message service to enable any computer on the network to submit a message destined for another

computer in such a way that the message will be delivered quickly and correctly. As the two computers are communicating there will be messages going back and forth similar to the types of messages between a user console and a computer on a time-shared system. It is in effect an ultra high speed postal system with little storage or buffering capability.

A typical usage of a network might be the preparation of a program on one computer, transmitting it to another computer for processing and finally transmitting the results back to the first computer for output on a line printer.

Within a network two types of message-switching may occur: circuit-switching and packet-switching. Circuit-switching is the classic approach where a complete path is established between the two parties for as long as they wish to communicate and is comparable to the telephone system.

Packet-switching is a method of working similar to the store-andforward technique used for telegraph message-switching in which

the communication called a message is broken up into smaller units

called "packets." Packet-switching is particularly suitable for

data transfers involving intermittent short bursts of data with

relatively long pauses between bursts. Packet-switching will be

discussed in greater detail in Chapter 2.

#### 1.1 Types of Networks

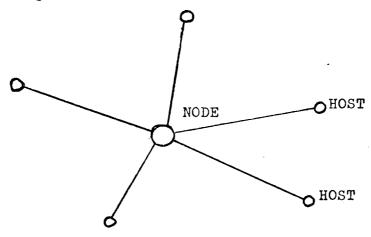

Centralised Networks are often called "star" networks because the

various computers are interconnected through a central unit as shown in Figure 1.1.

Figure 1.1 Centralised or star network

Figure 1.1 shows a centralised network as a set of point-topoint connections. An alternative structure is a multipoint

or multidrop line where several terminals or computers may use

one dedicated line.

This type of network requires that the capabilities of the central controlling unit far surpass those of the peripheral units or it requires that the central computer does little more than switch the various messages between the other computers connected to it. As may be seen, the major disadvantage of a centralised network is the vulnerability of the network to the failure of the central computer i.e. should the central computer incur a fault the entire network ceases to function.

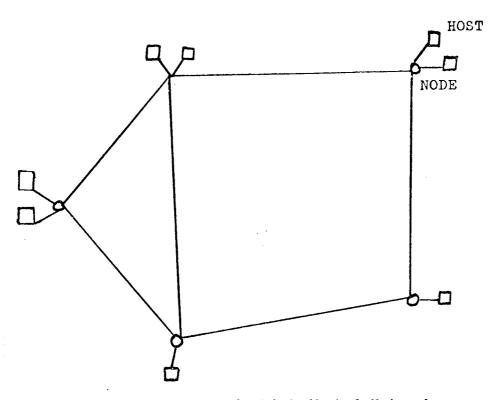

A distributed (or decentralised) network overcomes the disadvantage of the centralised network by having no central computer. The

responsibility for communication is shared among all the nodes in the system as shown in Figure 1.2.

Figure 1.2 Distributed Network

A message may have to pass through several nodes before reaching its final destination. The network is made more reliable by ensuring that each node is connected to at least two others. In the event of a connecting link failing communication may always continue along an alternative path. Even if a node fails, unaffected nodes can continue to function as long as the link remains operable.

ARPA is a distributed network but is not fully connected as the cost would be prohibitive, whereas MERIT is an example of a fully connected distributed network.

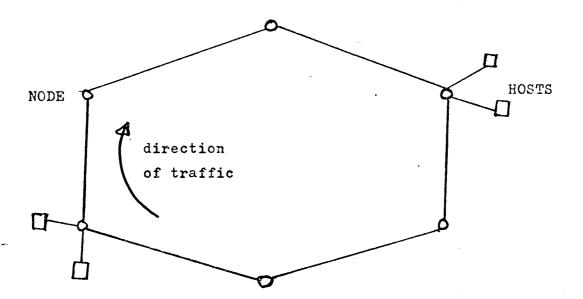

In a ring network, a ring or loop-type network is formed by a set of nodes. Any terminal or host computer wishing access is connected to one of the nodes as shown in Figure 1.3.

Figure 1.3 Ring Network

The nodes bridge their input and output lines with a shift register. The channel capacity of the ring is multiplexed into a series of time slots e.g. a 20 kilobits/second channel is divided into 20 slots each of 1000 bits. The time slots all flow in the same direction from node to node. All incoming messages are then put into a free slot as it comes around. A ring-switched network may consist of several rings. Neighbouring rings would be interconnected by a switching processor. Although ring networks are easy to design and cheap to build they have low reliability. Hayes and Sherman [1] discuss ring networks in greater depth.

## 1.2 Existing Networks

#### 1.2.1 ARPA

The Advanced Research Project Agency (ARPA) funded network is probably the most sophisticated network in existence [2-15].

Its primary goal is to make available the resources of the network to all users. Other design aims of ARPA are:

- 1) A communications cost of less than 30 cents per 1000 packets

(-1 megabits).

- 2) Average packet delays under 0.2 seconds through the network.

- 3) Capacity for expansion to 64 IMP's without major hardware or software redesign.

- 4) Average total throughput capability of 10-15 kilobits/second for all hosts at an IMP.

- 5) Peak throughput capability of 85 kilobits/second per pair of IMP's in an otherwise unloaded network.

- 6) Transparent communications with maximum message size of approximately 8000 bits and error rates of one bit in 10 12 or less.

- 7) Total network traffic 700-800 kilobits/second for a 20 IMP network.

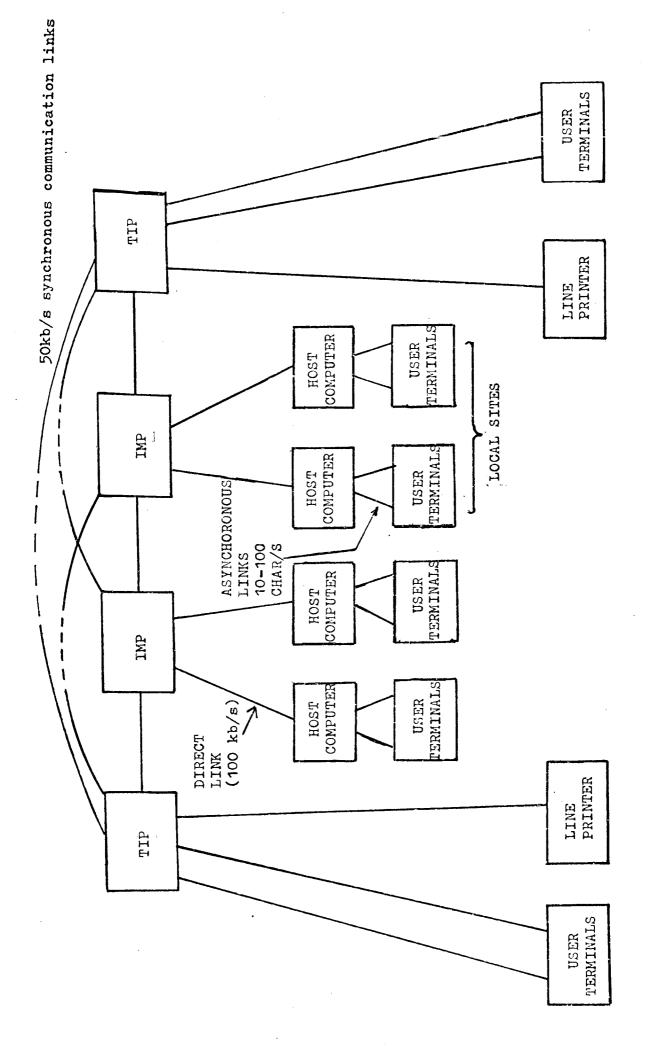

ARPA is a distributed network of heterogeneous computers and operating systems. Local computers (HOSTS) are linked to the network via Interface Message Processors which are generally called IMP's. IMP's are modified Honeywell DDP-516's with 12 k memory - 6 k memory is required by software support, the remaining memory is used for message and queue storage. Each node can store approximately 77 packets. Terminals can use the network directly via Terminal Interface Processors (TIP's) [7,11]. Figure 1.4 shows the general layout of a section of ARPA. The network provides store-and-forward communications. Internodel communications are provided via 50 kilobit full duplex leased lines. Reliability has been achieved through efficient euror-checking of each packet and the provision of two separate links from each node to

Figure 1.4 Functional Units of ARPA Network

protect against total link failure.

Each Host computer has a Network Control Program (NCP) whose function is to establish links, terminate links and control the flow of traffic.

When an IMP receives a message from a Host it breaks it up into "packets." Packets have a maximum size of 1008 bits, and each message consists of up to a maximum size of 8095 bits. Packets are then independently routed to the destination IMP where space has been reserved for reassembly before transmission to the receiving host.

As each packet is passed from IMP to IMP to reach its destination, the sending IMP retains a copy until an error check is carried out at the receiving IMP and a positive acknowledgement is sent back. On receipt of a packet an IMP must determine whether a packet has reached its destination or whether it needs to be transmitted further by checking the destination address.

Each IMP has the facilities for detecting communication failures, transmitting idling packets during the absence of normal traffic, and gathering performance statistics.

ARPA currently has over 40 nodes and over 80 hosts spread across

America to Hawaii (via satellite link) and a few locations in

Europe as shown in Figure 1.5. The hosts range from PDP-11's to

the ILLIAC 4 which are incompatible both in software and hardware.

ARPA network - logical map of hosts and nodes, July 1973 1.5 Figure

#### 1.2.2 Cybernet

CDC's CYBERNET [2,16], although not as sophisticated as ARPA needs to be mentioned since it was one of the first commercial networks offering its facilities to the public. It was built to connect CDC's existing computer centres to provide the following advantages:

- 1) Better reliability, users have access to an alternative computer in the event of a breakdown.

- 2) Greater throughput by allowing local work to be transferred to a less busy site. It also allows better load balancing with machines in different time-zones.

- 3) Better manpower utilization; allowing users to access one anothers programs and data bases.

- 4) Enhanced computer utilization through users choosing the best resources rather than local ones for the task in hand.

Cybernet is a distributed store-and-forward network composed of heterogeneous computers, mainly CDC 6600's and CDC 3300 linked by wideband lines across the U.S.A. The CDC 6600's, which constitute the primary computing element, are referred to as "centroids"; while the CDC 3300's serve as front end loaders and concentrators to the 6600's and are referred to as "nodes." Interactive and remote job submissions are supported by terminals and satellite computers. Cybernet communications employ switched, leased and satellite communications.

However, Cybernet cannot reconfigure itself and relies essentially

on hand-established terminal to computer, and computer to computer connections. Although alternative paths do exist, line failure in general necessitates human intervention.

#### 1.2.3 DCS

The Distributed Computer System (DCS) shown in Figure 1.6 is an experimental computer network being developed and constructed at the University of California at Irvine [2,17,18]. Its aims are: low cost, reliability, expansion capability and modest software development. However, the primary aim is to investigate the nature of distributed architecture in general. It is intended primarily to service mini to midi computers.

Figure 1.6 DCS network

The communications architecture is based on the Bell System TI technology (Pulse Coded Modulation on wideband of order 1.5-6.2

megabits) and fixed-length messages. The coaxical cable will initially give 2 megabits per second digital transmission but could be increased to the 6 megabit limit. Host computers are connected to the network via "ring interfaces" not computer nodes. DCS supports three classes of ring interfaces:

- 1) Computer support which could be a front end machine.

- 2) Terminal support.

- 3) Network of ring support.

Messages are sent to a process name and not to a real processor address. The process is identified by a general classification such as language file etc. Within each class are subclasses such as Basic, Fortran, PL/1 etc.

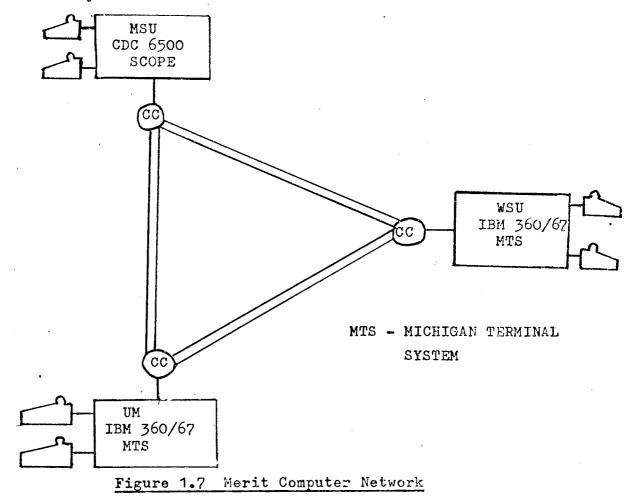

#### 1.2.4 MERIT

The Michigan Education Research Information Triad (MERIT) is a tripartite effort between the three largest universities in Michigan: Michigan State University, University of Michigan, and Wayne State University [2,19,21,22]. Its objective is similar to ARPA: namely resource-sharing.

Merit is a distributed network consisting of three nodes having three heterogeneous hosts which are connected to the network via Communications Computers (CC). The CC is a modified DEC PDP-11/20 with 16k 16 bit words of memory. The CC acts as a store-and-forward system enabling an alternative path to be chosen should a line fail. The Communications Computer Cperating

System (CCOS) requires 8k of memory, the remaining memory being used for message storing. Figure 1.7 shows the MERIT network layout.

Inter CC communications is provided initially by a group of 2000bps voice-grade lines for reasons of economy, low load and by the fact that they exist. As with ARPA after traversing each path the message is error-checked and an acknowledgement is sent for an error-free receipt.

The host/cc interface is capable of independently transmitting a variable-length data record to (from) the CC memory from (to)

the host computer, performing any memory alignment operation required by the different word configurations of the two processors. The host software in addition is simplified by the interface providing a multi-address facility permitting the host to treat the CC as several peripheral devices. Thus each user/task requesting use of the communications resource is allocated a dedicated pseudo-device.

#### 1.2.5 Octopus

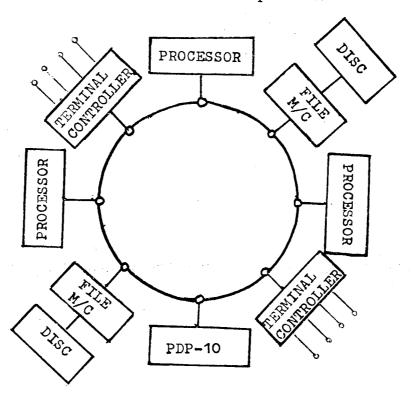

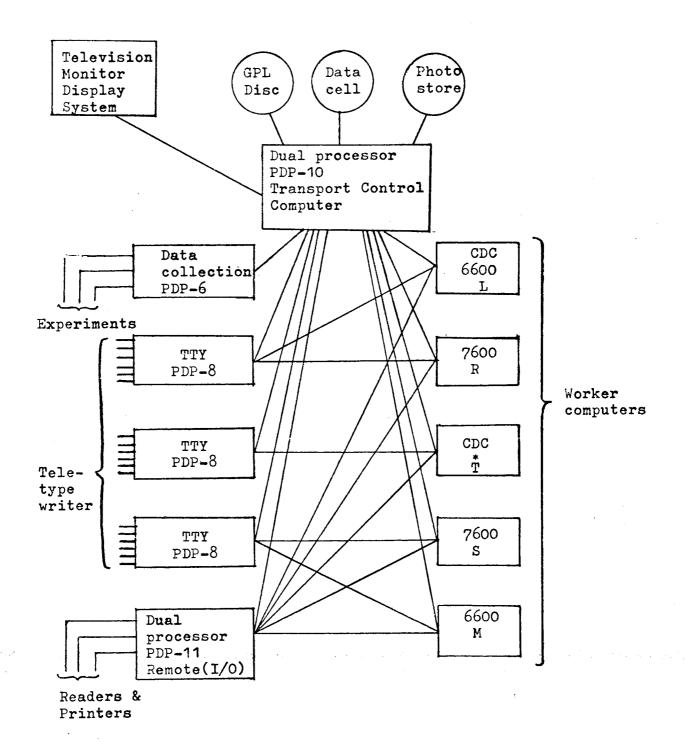

Octopus is a heterogeneous network developed at the Berkeley Laboratory of the University of California which became operational in 1964 [2,22]. The primary computer power is provided by two CDC 6600's, two CDC 7600's and a CDC STAR. All these "workers" operate as time-shared facilities. The network supports a centralised data base and a large variety of I/O devices which give the user a single access point to all computers.

The workers are interconnected via 12 megabit hard-wired lines and the communication system utilizes a store-and-forward protocol. The topology of OCTOPUS is shown in Figure 1.8.

The system is best viewed as two independent, superimposed networks:

1) File Transport Subnet which consists of a centralised network of the worker computers connected to the Transport Control Computer (a duplexed PDP-10) and the central memory system (disc, data cell, and photo store).

Figure 1.8 OCTOPUS network

2) Teletype subnet which is a distributed network consisting of the worker computers, 3 PDP8's (each of which can

service up to 128 T/T's and the Transport Control Computer.

A graphic display capability with distributed monitors is provided by the Television Monitor Display System (TMDS).

A third subnet exists to support remote I/O via a duplexed PDP-11.

### 1.2.6 TSS

The Time Sharing System (TSS) network is a distributed network of homogeneous computers developed in 1967 between IBM and some of its 360/67 customers [2,23]. The 360/67's use the IBM TSS/360 operating system. Some of the 360/67's operate as nodes for a local network consisting of 360's which appear as devices to the network not hosts.

The nodes are interconnected by 2000bps voice-grade lines and 40,800 bps leased lines. The voice-grade lines are interfaced to the IBM 360/67 by IBM 2701's and 2703's.

The communication software operates as an ordinary user program resident in the host computers which has to provide all programs such as store-and-forward, error-checking etc. This approach has the advantage of minimising extensive changes to the TSS/360 operating System. However, the penalty paid is that the communication software has to contend for resources on the

same basis as any other program. This results in the communications equipment not being used to maximum advantage.

Users access the network via CAM (Computer Access Method)

which is a specially developed set of procedure calls. A CAM

request will check on whether a connection exists to the destination computer; if not, one is established. Messages, which

may be up to 1k bytes long, are error-checked and acknowledged

on receipt or a retransmission request is made.

It is primarily a research network to investigate the advantages and disadvantages of general purpose networks. Load-sharing, remote service and dynamic file access are some of the features provided. Using homogeneous computers eases implementation problems since problems of different command languages, data structures, operating systems and machines are avoided.

#### 1.2.7 TUCC

The Triangle Universities Computation Centre (TUCC) has been operative since 1966. It is another joint venture between three major North Carolina Universities: Duke University, Noth Carolina State University and the University of North Carolina although many schools and colleges also enjoy the benefits of TUCC [2,24]. It is a simple central network supporting homogeneous IBM 360/40's and 360/75. The 360's are multiprogrammed for local batch work and to support the telecommunication requirements of the network. The network central

control is carried out by an IBM 360/75 which was replaced by an IBM 370/165 in 1972 to cope with the work load.

The three primary goals that the network had to satisfy were:

- 1) To provide economically adequate computing facilities to each institution.

- 2) To minimise system programming personnel.

- 3) To encourage greater cooperation between the three universities in the exchange of systems, programs and ideas.

The TUCC computer connects with the local sites via single leased wide band lines of 40,800 bps half duplex operation. The network has resulted in substantially greater computer facilities through economies of scale.

The networks that have been discussed show a wide range of architecture and approach that have employed in network design. There are many other networks including ACCNET [25], DATRAN [26], NPL [27] and the British Post Office's Experimental Packet-Switching Service [28]. Figure 1.9 shows a summary of existing network features.

Computer Networks may be justified for any reason or combination of reasons as given below:

- 1) Load balancing

- 2) Avoidance of data duplication

- 3) Avoidance of software duplication

- 4) Flexibility

- 5) Simplification of file backup

- 6) Ability to combine facilities

- 7) Conversion simplification

- 8) Enhancement of file security

- 9) Decreased system costs

- 10) Improved computer efficiency.

#### 1.3 Modelling Methods

There are two main techniques that may be used to analyse and evaluate the effects of proposed changes on network performance.

However, all methods including simulation have their limitation.

The first method involves using Stochastic queuing theory [43,44] requiring the derivation of a series of equations describing the network being examined. The system being studied consists of a continuous flow of information or items which are counted in aggregate rather than as individual items. Even for simple networks the resultant models tend to become extremely complex and rather stringent simplifying assumptions must be made in order to find solutions. A number of queueing models have been devised to analyse the characteristics of networks [29,30].

The alternative to queueing theory which is also widely

|                                       | 11                   | 1                   | 1                    | 1                   | 1                            | 1                      | 1                                            |

|---------------------------------------|----------------------|---------------------|----------------------|---------------------|------------------------------|------------------------|----------------------------------------------|

|                                       | ARPA                 | CYBERNET            | DCS                  | MERIT               | OCTOPUS                      | TSS                    | TUCC                                         |

| ORGANISATION                          | DIST-<br>RIBUTED     | DIST-<br>RIBUTED    | DIST-<br>RIBUTED     | DIST-<br>RIBUTED    | MIXED                        | DIST-<br>RIBUTED       | CENTRAL                                      |

| COMPOSITION                           | HETERO-<br>GENEOUS   | HETERO-<br>GENEOUS  | HETERO-<br>GENEOUS   | HETERO-<br>GENEOUS  | HETERO-<br>GENEOUS           | HOMO-<br>GENEOUS       | HOMO-<br>GENEOUS                             |

| NUMBER OF<br>NODES                    | <b>&gt;</b> 46       | 36                  | 9                    | 3                   | 10                           | 9                      | 4                                            |

| GEOGRAPHY OF<br>NODES                 | USA                  | USA                 | UC<br>IRVINE         | MICHIGAN            | LBL                          | USA                    | NORTH<br>CAROLINA                            |

| MACHINE<br>SIZE                       | MIXED                | LARGE               | MINI                 | LARGE               | LARGE                        | 360/67                 | 360                                          |

| COMMUNICATION<br>INTERFACE<br>MACHINE | HONEYWELL<br>DDP-516 | CDC 3300<br>PPU     | RING<br>INTERFACED   | PDP=11              | CDC<br>PPU                   | IBM<br>2701            | IBM<br>2701                                  |

| COMMUNICATION PROTOCOL                | MESSAGE<br>SWITHCED  | MESSAGE<br>SWITCHED | MIXED                | MESSAGE<br>SWITCHED | POINT<br>TO<br>POINT         | POINT<br>TO ·<br>POINT | POINT<br>TO<br>POINT                         |

| TRANSMISSION<br>MEDIUM                | LEASED<br>LINES      | LEASED<br>LINES     | TWISTED PAIR COAXIAL | TELPAK              | COAXIAL                      | DDD                    | TELPAK                                       |

| DATA RATE<br>bps                      | 50,000               | 100-<br>40,800      | 2.5 M                | 2,000               | 1.5-12<br>M                  | 2000<br>40,800         | 100 <b>-</b> 2 <b>400</b><br>40 <b>,</b> 800 |

| TRANSMISSION MODE                     | ANALOG               | ANALOG              | DIGITAL              | ANALOG              | DIGITAL                      | ANALOG                 | ANALOG                                       |

| MESSAGE<br>FORMAT                     | VARIABLE<br>LENGTH   | FIXED<br>LENGTH     | VARIABLE<br>LENGTH   | VARIAELE<br>LENGTH  | VARIABLE<br>LENGTH           | VARIABLE<br>LENGTH     | VARIABLE<br>LENGTH                           |

| MESSAGE<br>SIZE                       | 8095<br>BITS         | 1024<br>CHARS       | 900<br>BITS          | 240<br>CHARS        | 1208 or<br>3,780,000<br>BITS | 8192<br>BITS           | 1000<br>BYTES                                |

Figure 1.9 Features of Existing Networks

used, is to simulate the network [30,31,32]. Simulation allows modelling of steady state and time-dependent systems with relative ease and permits analysing transient conditions. Since no explicit equations need to be derived, a simulation may handle a large number of variables thereby enabling complex models to be handled more easily. In fact, where the number of variables is large, simulation may be the only course available. In order to develop a simulation model it is necessary to know the distribution of the various processes.

Simulation also permits discrete change models to be modelled easily which have been used widely to study communication networks. Discrete change models conceptualise the changes in the state of the system as discrete rather than continuous. Such network models have the following characteristics

- a) the system is defined by modules which operate on distinct parts of the model.

- b) packets flow through the network from one module to another, at each stage a specific function is performed before being passed onto the next.

- c) Each module has a limited capacity to process the packets, and therefore the packets may have to wait in a "queue" before reaching a particular module.

The main objective in discrete models is to examine the characteristics of the network and to determine the capacity of the system i.e. how many packets will pass through the network in

a given time. The main computational task consists of keeping track of where individual packets are at any given time,

moving them between routines, timing the moves and processing times at the modules.

Simulation techniques are limited only by the capacity of the computer but generally at a higher computational cost than queueing theory. Furthermore the results of a simulation tend to be in a form that is easier to interpret than those of queueing theory. To be of value, however, a simulation model must be accurate.

Bearing in mind that the network will be conceptualised as a discrete change model where transient conditions need to be studied, it was decided to carry out the investigation using a software simulation approach.

# 1.4 Objectives of Investigation

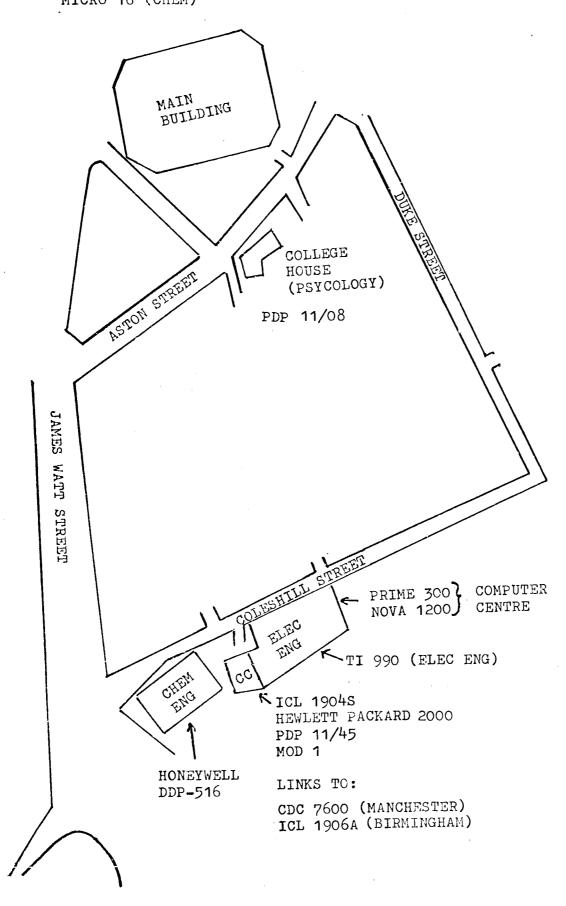

Figure 1.10 shows the location of computers at the University of Aston and the types available. The computers are drawn from a variety of manufacturers and are mainly incompatible both in hardware and software. Since many of these computers are underutilized and do not have the same facilities as other computers on site, it would be advantageous to join these computers on a network to enable other users to use the system during slack periods and allow all users to access the unique features of individual machines.

FIGURE 1.10 TYPE AND DISTRIBUTION OF COMPUTERS

AT ASTON UNIVERSITY

There are a number of fundamental questions to be answered in the process of designing computer networks. Major problems are the layout and sizing of connections between nodes i.e. where should a line go and what should its capacity be? What should the packet length be? What traffic load can the network sustain? These problems are difficult to answer because there are many possible combinations to choose from. A simulation model has therefore been developed to help in the investigation of the problem.

Packet switching communication systems have two fundamental goals in processing data - low delay and high throughput. The major modelling effort is concentrated on the study of the behaviour of messages queueing for access to the network. This seems a reasonable approach since in a packet switching network, messages experience delays as they are transmitted through the network and thus the queue lengths and speed with which messages are throughput are a reasonable performance measurement.

The areas of interest include the relative capabilities of the network, identification of specific limitations of the network and may be divided into three main areas:

- 1) Node parameters:

- a) effect of number of processor/memory modules

- b) effect of memory/processor speed

- c) memory module size

- 2) High level Network parameters:

- a) Number of nodes in network

- b) Number of hosts

- c) effect of line speeds

- 3) Low level Network parameters:

- a) effects of increasing mean packet length

- b) effects of changing ratio between different message lengths

- c) effect of increasing mean number of generating hosts

- d) effect of increasing packet length.

### CHAPTER TWO

### FUNCTIONAL ASPECT OF NETWORKS

### 2.1 Introduction

This chapter is concerned with developing some of the ideas introduced in the previous chapter. The purpose of this is to indicate some of the problems that will be encountered in this investigation. After discussing packet-switching and packet format, the functions of a node are presented with particular emphasis on message-handling and buffering, error control, flow control and routing. Finally Host-Node protocol is discussed.

### 2.2 Packet-Switching

Rather than provide channels on a user-pair basis, it would be much more efficient to provide a single high-speed channel to a large number of users which share it in some fashion. This brings into effect the "large numbers law" which states that with very high probability, the demand at any instant will be approximately equal to the sum of the average demand of that population." In this way the channel capacity required to support the user traffic may be considerably less than in the unshared case of dedicated channels. The important observation that can be made is that the full-time allocation of a fraction of the channel to each user is highly inefficient compared to the part-time use of the full capacity

of the channel (this is precisely the same idea as the notion of time-sharing).

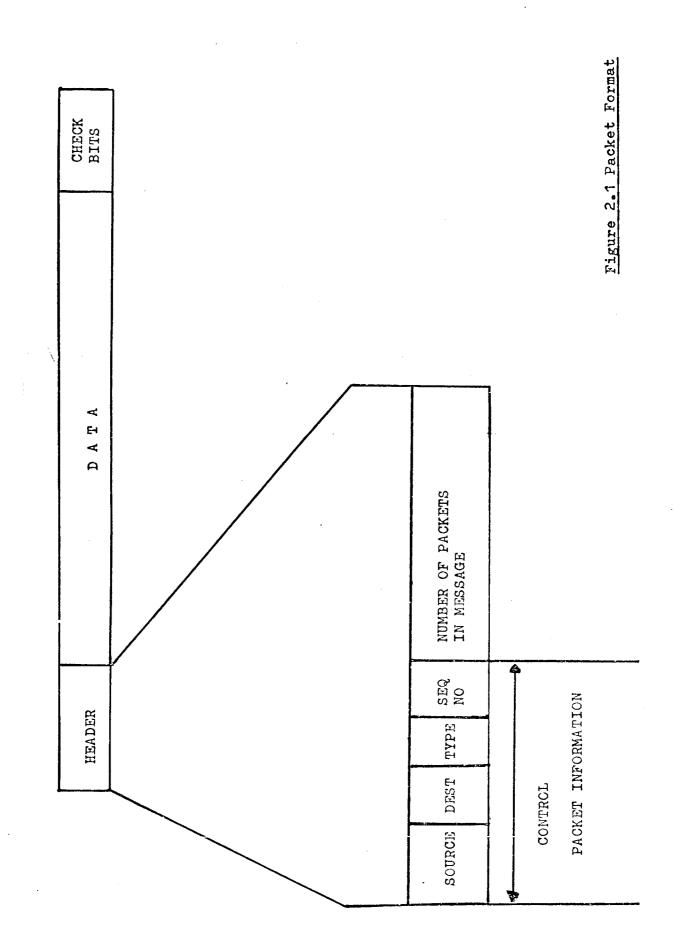

## 2.2.1 Packet Format [33,34]

Each packet is a group of control and data bits which is independently transmitted to find its way to the destination. The control bits contain addressing and processing information and have a fixed format while the data bits may have any format providing the total data bits can be carried as multiples of 8/16 bit bytes.

As shown in Figure 2.1 a typical packet would contain the following control information:

- 1) Source Address

- 2) Destination Address

- 3) Type of packet

- (a) Message

- (b) Acknowledgement

- (c) Special inter-nodal control messages giving status information concerning buffers, lines, and node status

- (d) "Send next packet!"

- 4) Packet Sequence No

only for data packets.

5) No of packets in a message

In each packet after the data, a sequence of check bits are added to enable the receiving node to check whether the packet has been transmitted error-free.

Packets therefore serve as the basic unit of information interchange between nodes. Their smaller size places a reduced demand on intermediate nodal storage and increases the likelihood of error-free transmission.

Consider as an example a data terminal in London wishing to use the services of a computer centre in Manchester. Using the switched DATEL services, a link would be established via the telephone network. That link would then be held for the duration of the complete transmission, even if there were periods during the call when no data was being transmitted. All conflict and allocation of resources must be resolved before the link can be established thereby permitting the traffic to flow with no conflict.

The alternative to this is packet-switching where the packet would be sent to the local packet-switching exchange (NODE). On arrival at the exchange it would be transmitted to the destination node by the most readily available route. During the transmission from source to destination there is no dedication of resources - conflicts being resolved as they are encountered. Internodal communication-lines are engaged only during packet transmission. During idle time the lines are available to other users. Should the most direct line be congested en route, the packet would be rerouted automatically through an alternative node. This ensures that:

- 1) Users are occupying long distant lines for the minimum of time.

- 2) High probability of rapid packet transfer.

- 3) Multiaddress or "broadcast" messages are facilitated.

- 4) Speed changing catered for allows terminals of different speed capabilities to communicate i.e. source transmission rate = reception rate of destination.

- 5) No dedication of resources.

- 6) Increases likelihood of error-free transmission.

- 7) More effective use of data channel.

An optimum packet length exists which depends on the application and the environment. If the packet is too long, errors will be so frequent that few data can be transferred; if the packet is too short, there is an unnecessary overhead, and too many control packets will be generated during the transaction.

### 2.3 Functions of a node

A node has four basic functions to perform:

- 1) Message handling and buffering.

- 2) Error control is required in four situations:

- (a) Out of sequence delivery of messages at the destination

- (b) Delivery of duplicate messages at the destination

- (c) Message delivery with errors

- (d) Message not delivered.

- 3) Flow control.

- 4) Routing.

## 2.3.1 Message handling and buffering [4.10]

The most important function of a node is to handle traffic from the local hosts that it services and traffic from neighbouring nodes.

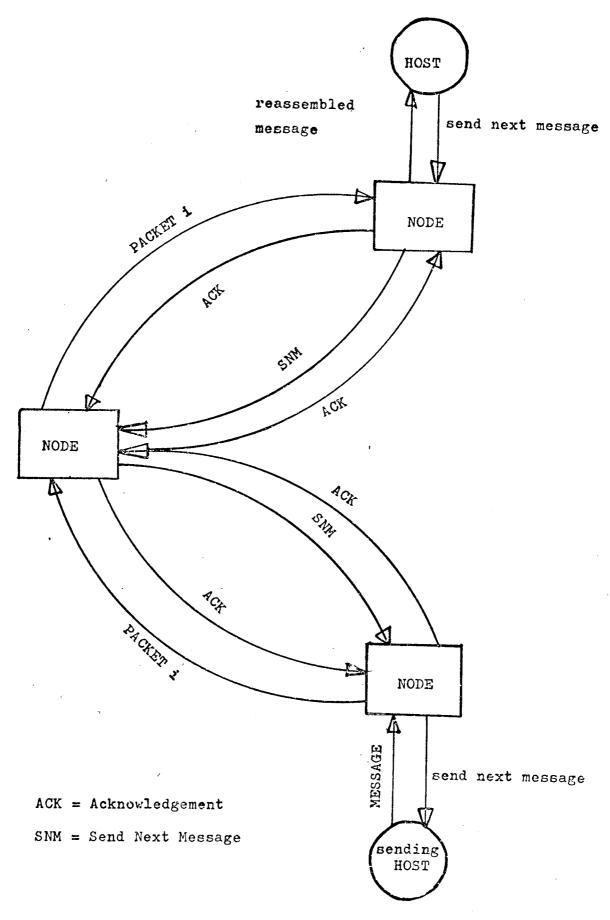

Communications between hosts is via sequences of messages, each of which is broken up into sub-messages called packets by the local node. Each message in ARPA can have a length of up to 8000 bits which is broken up into packets of 1000 bits length. Each of these packets is then independently transmitted by the network to the destination node which reassembles the packets into a single unit prior to handing it over to the destination host. Along the route each node retains a copy of a packet until a positive acknowledgement is received indicating error-free transmission and acceptance (e.g. the node is not too busy). Should an acknowledgement not be received within a reasonable time say 0.1 seconds it is retransmitted, possibly along another line. The examination of the packet header by the node will determine whether a packet is at the destination node or whether it needs further transmission.

When the destination node has received all the packets in a message, it must put them into the correct order, strip off the header from each packet and put a leader on the message, identifying the source host. Once the host has received the message it will issue a "Ready for Next Message", which is

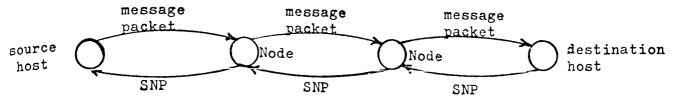

transmitted back to the source host where it also serves as an indication that the message was correctly received. Figure 2.2 illustrates packet-switching between host computers.

If buffer handling is made simple then fast processing will be achieved and the program size will be kept to a minimum. The number of buffers should be such that all incoming traffic can be stored to enable the lines to be used to full capacity.

Fixed buffer sizes simplify the design and speed up the handling operation. Variable packet lengths lead to inefficient utilization of network resources (buffers etc.).

The high level network avoids an extensive message-buffering problem by preventing any host sending a message to any other host that is in no condition to receive messages.

If a host is to be effective on the network, it must be willing to receive and acknowledge messages with extremely little

delay. Then the major burden of message buffering is on the

host computers themselves.

### 2.3.2 Error Control

The node has full responsibility for providing error control.

Four situations can arise which the node must handle.

Allowing messages to be multipacket and sent along independent routes will lead to the packets arriving at the destination node out of sequence. At the destination node the packets

Figure 2.2 Packet Switching between host computers

must be reassembled into the correct sequence before being handed over to the destination host. Assigning packet sequence numbers would enable this to be carried out. The situation where a host pair could have several messages on the system could arise but is best avoided as this further complicates the network i.e. with each host pair allowed one message, sequencing would occur naturally.

Should an acknowledgement be missed somewhere along the route it is possible that a duplicate packet would be retransmitted. The provision of sequence numbers for each packet in the message would enable the message to be correctly reassembled at the destination.

Noise is the primary cause of errors on communication channels. Error handling is simply achieved by error detection (e.g. cyclic redundancy code carried out on each packet) and retransmitting the packet if necessary when an acknowledgement is not received through an erroneous packet.

Each transmitted message will now be accurately delivered to the intended destination through reliable network design. Should a message fail to get through, simple end-to-end retransmission would protect against the occurence of this situation.

## 2.3.3 Flow Control

It is clear that any network has a limit to the amount of traffic that it can support. Should traffic rise over a certain level, it must be rejected or the network will grind to a halt. When a network reaches a situation where it must reject traffic then it is said to be "congested" or "logically deadlocked" where traffic movement has stopped. To prevent these situations occuring good flow control techniques are required. The provision of mass storage in the nodes could greatly increase the mean time to congestion. However, more storage alone cannot in general prevent congest-The network must provide a certain amount of buffering between the source and destination host, preferably equal to the band-width of the channel times the round trip time over the channel. Flow control is necessary to prevent messages from entering the network for which there is no buffering available.

As with road traffic, congestion may be expected to start at one point in the network and spread as the queues fill and links between nodes are blocked. The workload a network can take will be increased through good routing. Eventually, a limit will be reached where several lines or nodes block simultaneously.

Congestion control methods can be classified as "local" or "end-to-end". Local control is applied in a subnet on

information passed between nodes. Neighbours inform each other of traffic delays experienced, or may request reductions or return to normal traffic over certain links.

A user who is contributing to the overload may be some distance away from the point where congestion is occurring and local control methods may have to spread some way before action is taken.

End-to-end control makes use of the notional links that exist between subscribers. Under heavy loading data rates of certain links may be reduced and new links may be refused.

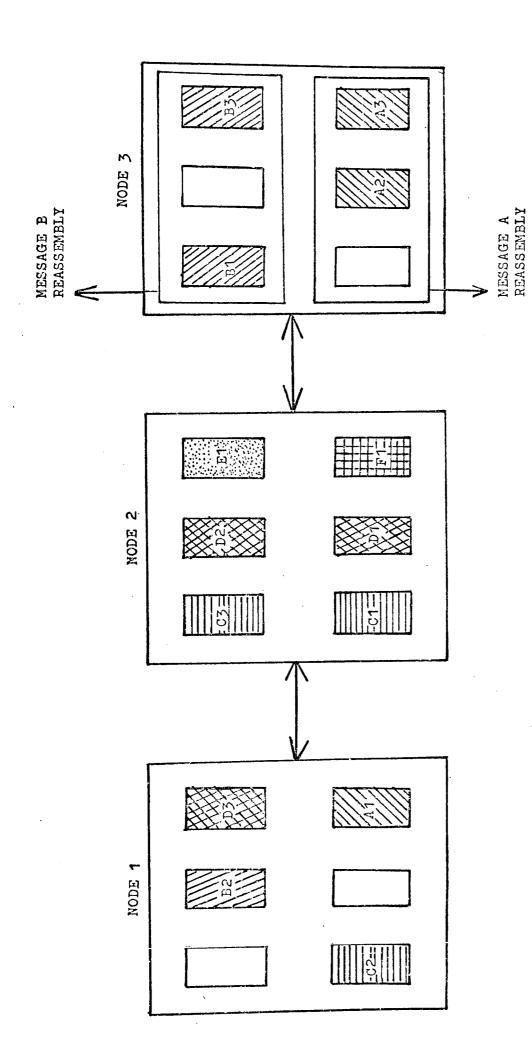

Two types of deadlocks may occur known as "reassembly lockup" and "store-and-forward lockup" which occur with multi-packet messages. Reassembly lockup is the situation where the remaining packets of a partially reassembled message are prevented from reaching the destination node by other packets in the network that are waiting for reassembly space at that destination to become free. Thus the first message cannot be completed and the reassembly space freed. In the second case of store-and-forward lockup, packets interfere with each other by tying up buffers in such a way that none of the packets are able to reach the destination although the destination has room to accept arriving packets.

Figure 2.3 shows the problem schematically. Node ! is sending

Figure 2.3 Reassembly Lockup

a multipacket message to node 3. Node 3 has devoted its buffers to partially reassembled messages A and B. Since all the buffers are tied up to messages A and B, the node can only free space when the remaining packets have been received from node 1. This is reassembly lockup. Packets A1 and B2 cannot get through since node 2 is in a store-and-forward lockup containing packets of which none are destined for node 3. Node 3 will therefore never complete its message-reassembly.

ARPA solves this problem by not permitting any multipacket message onto the network until the destination IMP has reserved reassembly storage. On receipt of the first packet from a host a control message is sent to the destination node requesting reassembly storage. When an acknowledgement has been received the IMP takes the remaining packets of the multipacket message from the host. This strategy will ensure that message D in node 2 could be reassembled.

An incomplete message at node 3 could be discarded at this point, since eventually a copy of the message would be retransmitted from the source host. The source host could be informed of this move.

Another solution would be to use overflow buffers thus ensuring that one packet at least would reach the destination. The

packet to be sent could be selected randomly. The receiving node

would acknowledge the packet if it was useful. If no acknowledgement is received another packet would be tried.

One node could take charge in this situation and try to sort things out. However, this solution would further increase the traffic and the controller itself would be vulnerable to failure.

The problem could be further eased by only allowing one message between host pairs at any time. The acceptance of the message by the destination host would be followed by a "Ready for next message." This solution would prevent the overloading of a node of host. Of course, it is assumed that some users would be transmitting messages rather than many users transmitting single packets coincidentally.

Davies [35] suggested that congestion could be prevented by placing a limit on the total number of packets in the net-work. Since data-carrying packets must be created and destroyed, the balance is kept by using empty packets. Thus the arrival of a normal data-carrying packet at its destination would result in its replacement in the network by an "empty" packet. Similarly, when data is ready to enter the network, an empty packet must be found to be replaced by a new data-carrying packet.

This constant group of packets can, by analogy, be compared to a gas composed of molecules in perpetual motion. Packets

will arrive and leave each node in the network at a roughly constant rate, regardless of the data traffic. All packets will eventually visit each node due to the randomness of the motion.

In order to keep the empty packets moving around the network some rule is needed. The rule should have a random element. Therefore, in its simplest form, a destination node could be chosen at random. When the empty packet arrives at the specified destination address it will be used by any data awaiting transmission. Should no data be waiting, a new destination address would be chosen and the packet would try elsewhere. When a data-carrying packet arrives at its destination, it would clearly be sensible to give data waiting at that node priority to use the empty packet rather than sending it randomly back into the network. Further efficiency could be gained by retaining a small store of empty packets at each node.

Should any traffic be offered beyond its capacity, the network would reject it until empties were created to resume normal operation.

Although the Isarithmic Network is quite attractive it does suffer from three serious problems:

1) Even though a rule exists for moving empty packets around the network, local congestion could still occur

due to the random element of distribution i.e. packets could collect at one node.

- 2) Some of the empty packets are required for control information thus reducing the effective number of usable packets.

- 3) It is as vulnerable as a central processor in a star network. If a node failure occurred the network could steadily gain or lose packets.

## 2.3.4 Routing [4,10,36]

Good routing strategies will ensure that message delay in the network is minimised. Message delay is the time taken to send a message from source to destination. A good routing strategy will also be adaptive to changing traffic levels and changing network topology in the event of a failure.

Each node applies some routing technique to decide the next link that the packet must travel over. In a distributed network the node will have to make a decision based on information it currently holds about the state of its neighbours, together with local information regarding the state of buffers and lines.

Perhaps the simplest strategy is fixed routing where packets from host i to host j always take the same route. The poor adaptability of fixed routing may be overcome by increasing the route reliability.

Random routing, which takes no account of the destination tends to give long average delays although they are very adaptive.

A simple strategy would be for each node handling a packet to send it along the current estimate of the shortest route to the destination. It is not enough to base a strategy solely on the local information such as internal queue lengths. However, it is a simple matter for each node to inform its neighbours of its state and from this all nodes can compute the current shortest path.

Since routing information itself suffers from a time delay, raw data such as current queue lengths are not enough to accurately characterize traffic flow. Some sort of averaging procedure must be employed in order to effectively select the shortest route and help to predict in advance where a possible traffic build-up could take place.

One scheme used on ARPA is to send packets along that line with the minimum estimated time delay to the destination. The time delay information is updated every 0.5 seconds using information from the nodes' neighbours regarding minimum time delays together with internal estimates of the delay to each neighbour. Should the traffic flow increase heavily this strategy may become inefficient due to the fact that information of queue lengths may change faster than the information

can be distributed.

ARPA used a more intricate scheme to overcome the inefficiency of the last algorithm during heavy traffic. The packets are now routed down the path with the fewest nodes and which have excess capacity. If that path becomes full then the one with the next fewest nodes and excess capacity is chosen.

EPSS [36] used an Alternative-Routing strategy. A table is accessed which gives the next path that must be taken. Should this path be congested the second choice is tried and so on until all choices are exhausted. Should there be no path, failure routines are invoked. To determine routing the node is restricted to the following information:

- a) Packet destination derived from packet header.

- b) The node from which the packet has just been received.

- c) The current queue length for each route.

- d) Which of the routes are the faster intercomputer routes.

- e) The packet source derived from the packet header.

- (b), (c) and (d) are used to determine whether the current choice is satisfactory.

This type of strategy is deterministic in that action is taken on traffic information only when route queues exceed a preset threshold.

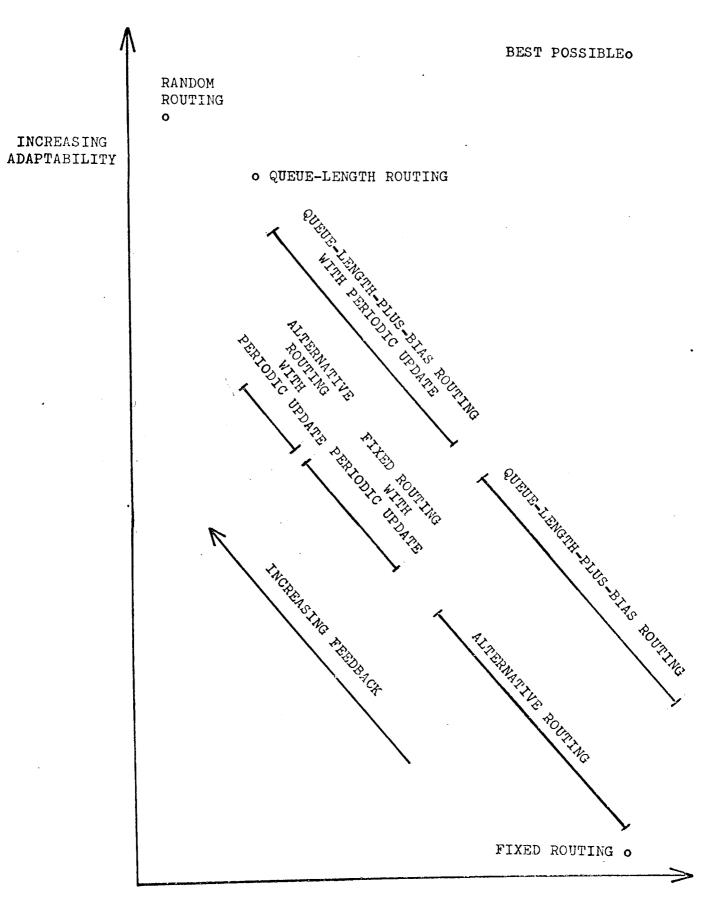

Figure 2.4 shows the relative merits of each of the strategies.

DECREASING AVERAGE PACKET DELAY

Figure 2.4 Comparison of different Routing Strategies

Two of the strategies have not been discussed. Queue-length routing transmits packets on the route with the shortest queue, regardless of packet destination. This gives very long delays compared with fixed routing.

Queue-Length-Plus-Bias is a compromise between the short average delay of fixed routing and the adaptability of the last strategy. The route selection is based on the evaluation of a function of queue lengths and bias for each available route. The bias terms are preset constants whose values import a gross traffic-flow pattern. An example of such a function, f, is

f[(bias term for route) - k(queue length for route)],

where k is a constant. The route selected is the one whose

function value has the largest numerical value. Under low

traffic conditions, the system reverts to a fixed route strategy,

but as traffic builds up, so the system adapts to equalise the

imbalance of route usage.

Eventually, as traffic levels increase, the re-routing of packets can no longer prevent congestion, and the network must reject traffic offered to it.

# 2.4 Host-Node Protocol

A number of questions need to be asked regarding the relationship of the host to its node. What tasks shall be performed by each? What constraints will one place on the other? What

## dependence shall the node have on its host?

The following tasks must be carried out:

- 1) Breaking up a long transaction into message blocks so that the length of the message is within the networks constraints (8000 bits on ARPA).

- 2) Formatting and code-converting the message blocks into a standard format acceptable to the network.

- 3) Attaching a header to each message block giving address and control information.

- 4) Attaching a trailer with error-checking information to each message block.

- 5) Storing the unacknowledged messages and/or message blocks for possible retransmission.

- 6) Reassembling received message blocks into messages.

- 7) Breaking the message blocks into packets.

- 8) Preceding each packet with a header.

- 9) Adding a trailer to each packet.

- 10) Storing the unacknowledged packets for possible retransmission.

- 11) Reassembling received packets into message blocks.

- 12) Controlling the input rate to avoid congestion.

On ARPA tasks 1-6 are carried out by the host while the remaining functions are the responsibility of the node. ARPA[4] was guided by the following principles:

1) The node should function as a communication system whose primary task is the reliable transfer of bits from

a source to a destination. Bit transmission should be sufficiently reliable and error-free to remove the need for special precautions (such as storage for retransmission) on the part of the host.

2) The node operation should be completely autonomous. Since the node must function as a store-and-forward system, it must not be dependent on its local host. The node must continue to function irrespective of the correct functioning of the host. So the node must not depend on the host for buffer storage or program reload. Also the host must not be able to change the logical characteristics of the node.

The general philosophy of host programming adopted by many networks is that network features are extensions and additions to the operating system and not changes to develop compatible software [21]. This is the principle of host autonomy. The connection between a pair of processes appears as an I/O device in each host. This respect for individuality ensures that the unique resources of the host are not only preserved for local use but also for global use on the network. The imposition of unnecessary commonality may simplify network structure but would probably stifle interest.

### CHAPTER THREE

### NETWORK PHILOSOPHY

### 3.1 Introduction

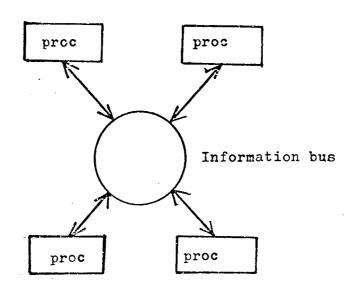

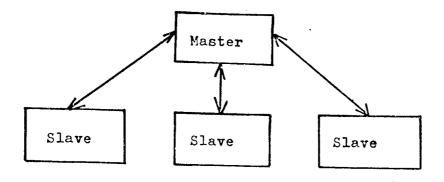

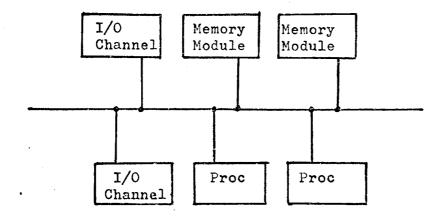

This chapter is concerned with the philosophy of the proposed network which will be later simulated. After an introduction to microprocessors, methods of organising microprocessors into multicomputer and multiprocessor systems are discussed. An outline is given into ways of organising microprocessors to achieve better computer reliability.

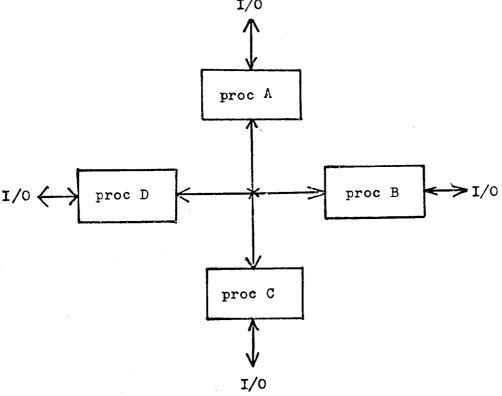

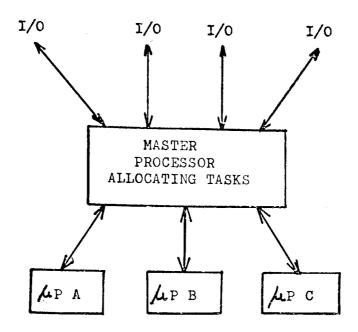

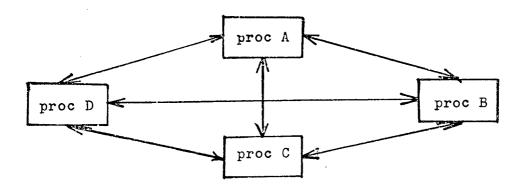

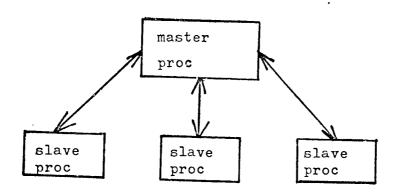

The architecture of the node centres on a multi-microprocessor system operating under amaster processor. The organisation of the node together with the functions of the command and slave processes are described.